- 您现在的位置:买卖IC网 > PDF目录256054 > BU-65843F3-200 (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 PDF资料下载

参数资料

| 型号: | BU-65843F3-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| 封装: | 0.880 INCH, CERAMIC, QFP-80 |

| 文件页数: | 40/75页 |

| 文件大小: | 532K |

| 代理商: | BU-65843F3-200 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

45

Data Device Corporation

www.ddc-web.com

BU-65743/65843/65863/65864

D-06/04-0

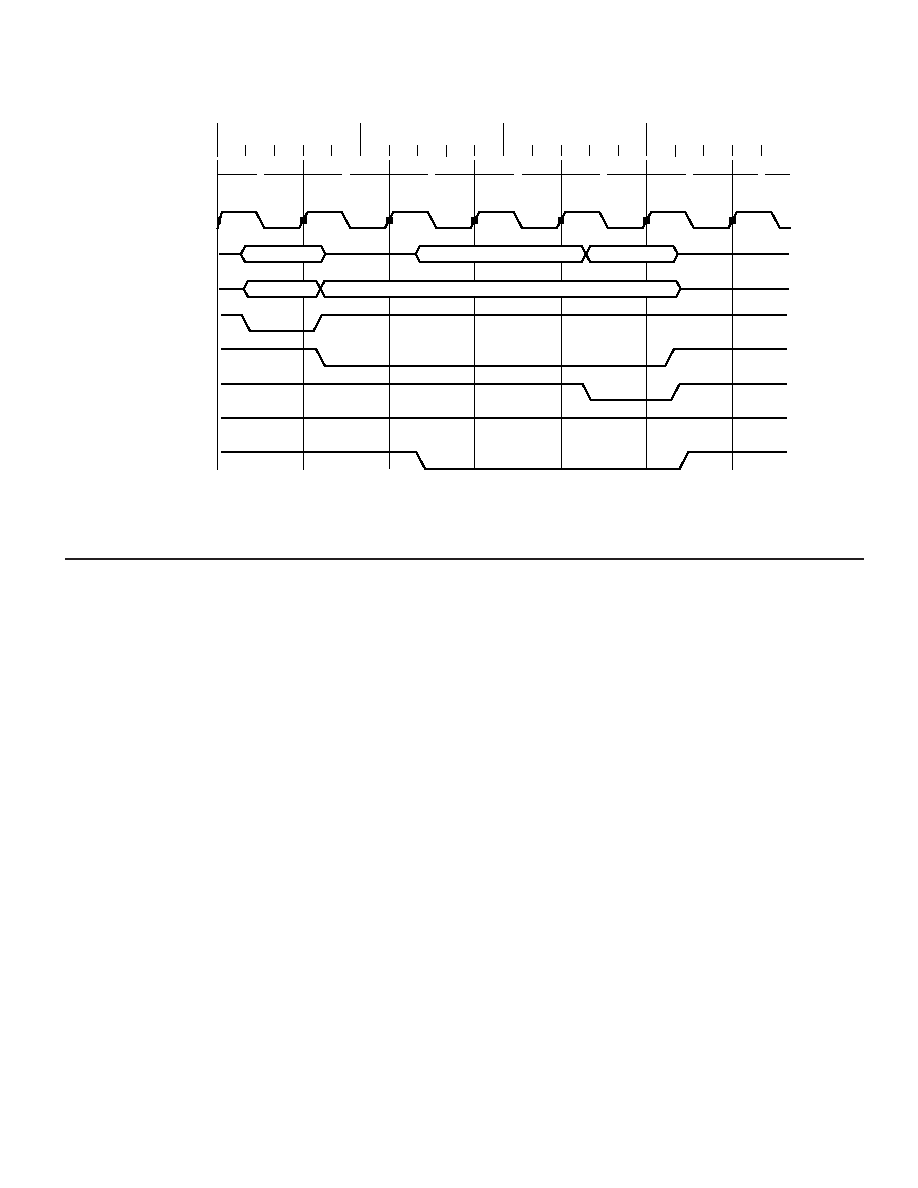

FIGURE 15. PCI READ OF PCI-ACE IF REGISTERS (BAR1 800-81CH)

1

2

3

4

5

6

7

PCI memory read from PCI-ACE interface register space (BAR1 800-81Ch)

ADRS

DATA

BYTE ENABLES

6h

0ns

50ns

100ns

150ns

I

PCICLK

IO

AD

I

C/BE[3:0]#

I

FRAME#

I

IRDY#

O

TRDY#

O

STOP#

O

DEVSEL#

Note that one of the conditions for enquing a DRR is that the

write FIFO must be empty. For efficient use of PCI bus band-

width, the driver software should be written such that it checks

the FIFO condition (BAR1 800-81CH registers are directly read-

able, bypassing the DRR mechanism) before reading from the

other PCI Mini-ACE Mark3/Micro-ACE TE locations. If the FIFO

is not empty (BAR1 800h bit 30 is the FIFO not empty flag) and

a read is attempted, the bus master will be using PCI bandwidth

repeating the read request while the FIFO empties, BEFORE the

read request is actually enqued as a DRR.

When reading ACE memory (BAR0), any combination of byte

enables is supported, but the PCI Mini-ACE Mark3/Micro-ACE

TE will drive the entire word onto the AD lines when only a sin-

gle byte enable in the word is asserted.

When reading ACE registers (BAR 00-FCh), byte enable combi-

nations where only a single byte within a word is requested will

cause the PCI Mini-ACE Mark3/Micro-ACE TE to terminate the

transaction with a target abort. The PCI Mini-ACE Mark3/Micro-

ACE TE will drive all zeros onto the AD lines if only the upper

word byte enables or no byte enables are asserted.

With relation to actual timing, PCI double word reads of ACE

memory (BAR0) will take longer to complete than single word

ACE memory reads because the internal ACE memory data path

is 16 bits wide. In addition, read cycles will take longer to com-

plete with slower ACE clocks. See Table 63 for min/max formulas

for calculating completion time for the various types of reads.

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65863F8-310 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BU-61559D1-330L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-380L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-530W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-560 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BU-65-9 | 功能描述:测试电夹 HEAVY DUTY LARGE JAW GATOR CLIP WHITE RoHS:否 制造商:Pomona Electronics 类型:Minigrabber clip 颜色:Black |

| BU6650NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX_11 | 制造商:ROHM 制造商全称:Rohm 功能描述:3ch CMOS LDO Regulators |

| BU6650NUX-TR | 功能描述:低压差稳压器 - LDO LDO REG 0.2A 8PIN 2.8V 2.8V 1.8V RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| BU6651NUX | 制造商:ROHM 制造商全称:Rohm 功能描述:High-speed Load Response Full CMOS LDP Regulators |

发布紧急采购,3分钟左右您将得到回复。