- 您现在的位置:买卖IC网 > PDF目录256005 > BX80532KC3000D (INTEL CORP) 3000 MHz, MICROPROCESSOR PDF资料下载

参数资料

| 型号: | BX80532KC3000D |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 3000 MHz, MICROPROCESSOR |

| 文件页数: | 10/129页 |

| 文件大小: | 1640K |

| 代理商: | BX80532KC3000D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页

Intel Xeon Processor with 512 KB L2 Cache

Datasheet

107

7.4.2

Scratch EEPROM

Also available in the memory component on the processor SMBus is an EEPROM which may be

used for other data at the system or processor vendor’s discretion. The data in this EEPROM, once

programmed, can be write-protected by asserting the active-high SM_WP signal. This signal has a

weak pull-down (10 kW) to allow the EEPROM to be programmed in systems with no

implementation of this signal. The Scratch EEPROM resides in the upper half of the memory

component (addresses 80 - FFh). The lower half comprises the Processor Information ROM

(address 00 - 7Fh), which is permanently write protected by Intel.

7.4.3

PIROM and Scratch EEPROM Supported SMBus Transactions

The Processor Information ROM (PIR) responds to two SMBus packet types: Read Byte and Write

Byte. However, since the PIR is write-protected, it will acknowledge a Write Byte command but

ignore the data. The Scratch EEPROM responds to Read Byte and Write Byte commands. Table 45

diagrams the Read Byte command. Table 46 diagrams the Write Byte command. Following a write

cycle to the scratch ROM, software must allow a minimum of 10ms before accessing either ROM

of the processor.

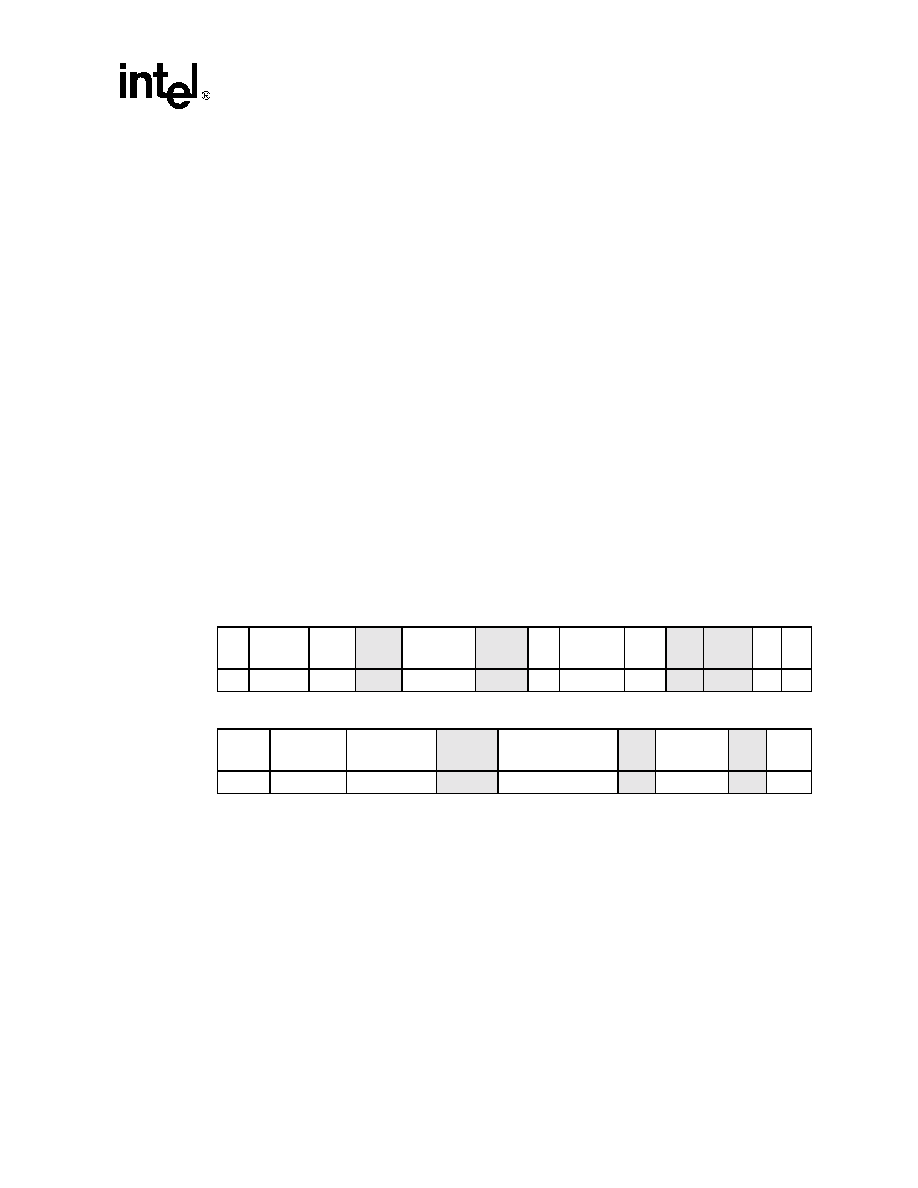

In the tables, ‘S’ represents the SMBus start bit, ‘P’ represents a stop bit, ‘R’ represents a read bit,

‘W’ represents a write bit, ‘A’ represents an acknowledge (ACK), and ‘///’ represents a negative

acknowledge (NACK). The shaded bits are transmitted by the Processor Information ROM or

Scratch EEPROM, and the bits that aren’t shaded are transmitted by the SMBus host controller. In

the tables the data addresses indicate 8 bits.The SMBus host controller should transmit 8 bits with

the most significant bit indicating which section of the EEPROM is to be addressed: the Processor

Information ROM (MSB = 0) or the Scratch EEPROM (MSB = 1).

7.4.4

SMBus Thermal Sensor

The processor’s SMBus thermal sensor provides a means of acquiring thermal data from the

processor. The thermal sensor is composed of control logic, SMBus interface logic, a precision

analog-to-digital converter, and a precision current source. The sensor drives a small current

through the p-n junction of a thermal diode located on the processor core. The forward bias voltage

generated across the thermal diode is sensed and the precision A/D converter derives a single byte

of thermal reference data, or a “thermal byte reading.” The nominal precision of the least

significant bit of a thermal byte is 1 °C.

The processor incorporates the SMBus thermal sensor and thermal reference byte onto the

processor package as was previously done on Intel

Xeon processor family. Upper and lower

thermal reference thresholds can be individually programmed for the SMBus thermal sensor.

Comparator circuits sample the register where the single byte of thermal data (thermal byte

Table 45. Read Byte SMBus Packet

S

Slave

Address

Write

A

Command

Code

AS

Slave

Address

Rea

d

A

Data

///

P

17-bits

1

18-bits

1

7-bits

1

8-bits

1

Table 46. Write Byte SMBus Packet

S

Slave

Address

Write

A

Command Code

AData

AP

17-bits

1

18-bits

11

相关PDF资料 |

PDF描述 |

|---|---|

| BU-65843F3-110 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP80 |

| BP83C51FA-1 | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PDIP40 |

| BU-61559D1-240S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-240 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

| BU-61559D1-290K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP78 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX80532KC3000H | 制造商:Intel 功能描述:MPU XEON NETBURST 64-BIT 0.13UM 3GHZ - Boxed Product (Development Kits) |

| BX80532KE2000D | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2GHZ - Boxed Product (Development Kits) |

| BX80532KE2000DU | 制造商:Intel 功能描述:XEON 2.0GHZ 533FSB 1U - Boxed Product (Development Kits) |

| BX80532KE2400DSL73L | 制造商:Intel 功能描述: |

| BX80532KE2400E | 制造商:Intel 功能描述:MPU XEON PROCESSOR NETBURST 64-BIT 0.13UM 2.4GHZ - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。