- 您现在的位置:买卖IC网 > PDF目录298893 > BX805555080A (INTEL CORP) 64-BIT, MICROPROCESSOR, BGA771 PDF资料下载

参数资料

| 型号: | BX805555080A |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, MICROPROCESSOR, BGA771 |

| 封装: | LGA-771 |

| 文件页数: | 87/104页 |

| 文件大小: | 3690K |

| 代理商: | BX805555080A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页当前第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

Dual-Core Intel Xeon Processor 5000 Series Datasheet

83

Features

7

Features

7.1

Power-On Configuration Options

Several configuration options can be configured by hardware. The Dual-Core Intel Xeon

Processor 5000 series samples its hardware configuration at reset, on the active-to-

inactive transition of RESET#. For specifics on these options, please refer to Table 7-1.

The sampled information configures the processor for subsequent operation. These

configuration options cannot be changed except by another reset. All resets reconfigure

the processor, for reset configuration purposes, the processor does not distinguish

between a “warm” reset (PWRGOOD signal remains asserted during reset) and a

“power-on” reset.

Notes:

1.

Asserting this signal during RESET# will select the corresponding option.

2.

Address pins not identified in this table as configuration options should not be asserted during RESET#.

3.

This mode is not tested.

7.2

Clock Control and Low Power States

The Dual-Core Intel Xeon Processor 5000 series support the Enhanced HALT

Powerdown state in addition to the HALT Powerdown state and Stop-Grant states to

reduce power consumption by stopping the clock to internal sections of the processor,

depending on each particular state. See Figure 7-1 for a visual representation of the

processor low power states.

The Enhanced HALT state is enabled by default in the Dual-Core Intel Xeon Processor

5000 series. The Enhanced HALT state must remain enabled via the BIOS for the

processor to remain within its specifications. For processors that are already running at

the lowest core to bus ratio for its nominal operating point, the processor will transition

to the HALT Powerdown state instead of the Enhanced HALT state.

The Stop Grant state requires chipset and BIOS support on multiprocessor systems. In

a multiprocessor system, all the STPCLK# signals are bussed together, thus all

processors are affected in unison. The Hyper-Threading Technology feature adds the

conditions that all logical processors share the same STPCLK# signal internally. When

the STPCLK# signal is asserted, the processor enters the Stop Grant state, issuing a

Stop Grant Special Bus Cycle (SBC) for each processor or logical processor. The chipset

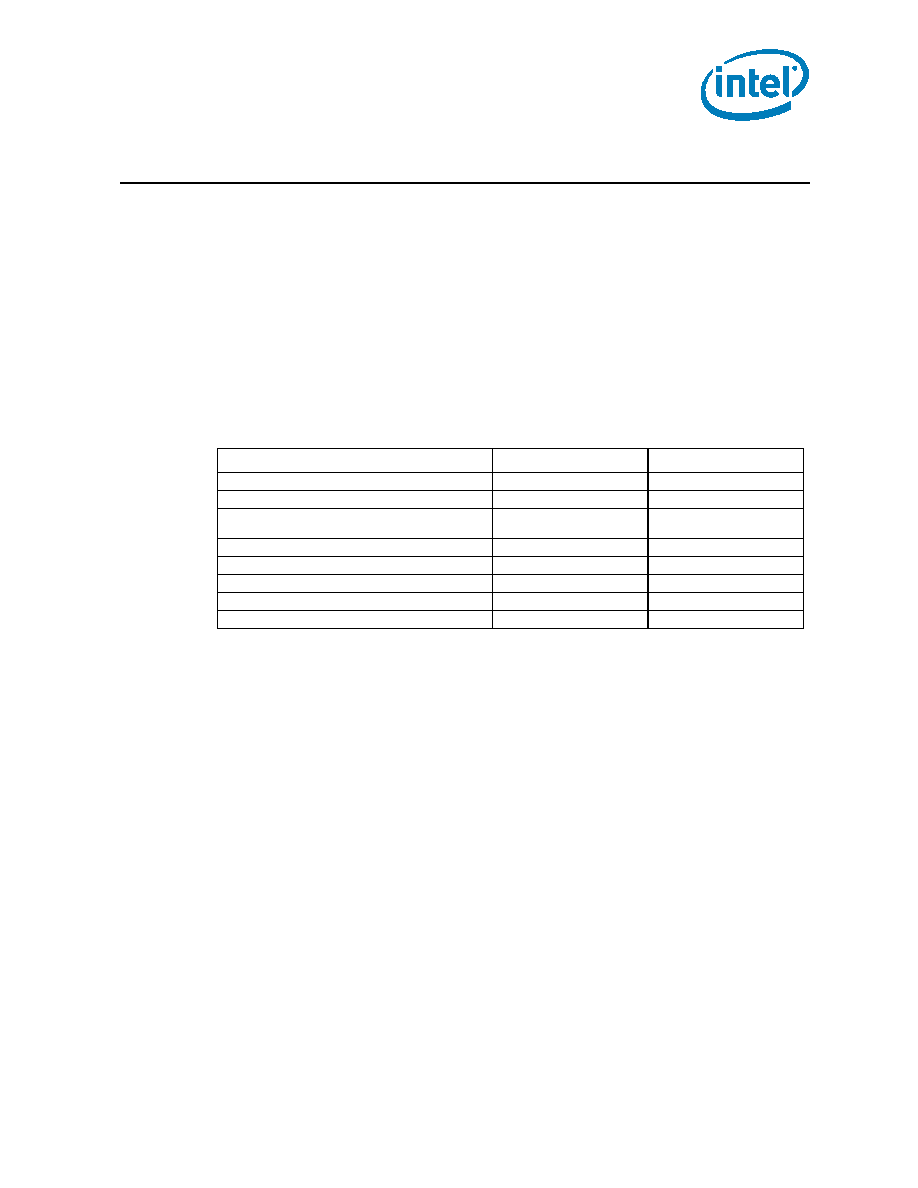

Table 7-1.

Power-On Configuration Option Lands

Configuration Option

Land Name

Notes

Output tri state

SMI#

1,2

Execute BIST (Built-In Self Test)

A3#

1,2

In Order Queue de-pipelining (set IOQ depth to

1)

A7#

1,2

Disable MCERR# observation

A9#

1,2

Disable BINIT# observation

A10#

1,2

Disable bus parking

A15#

1,2

Symmetric agent arbitration ID

BR[1:0]#

1,2

Force single logical processor

A31#

1,2,3

相关PDF资料 |

PDF描述 |

|---|---|

| BX805555030P | 64-BIT, MICROPROCESSOR, BGA771 |

| BX80557E2140 | MICROPROCESSOR, PBGA775 |

| BXM80526B600128 | 64-BIT, 600 MHz, MICROPROCESSOR, PBGA495 |

| BXM80526B700128 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

| BXM80526B700 | 64-BIT, 700 MHz, MICROPROCESSOR, CPGA495 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| BX805565120P S L9RY | 制造商:Intel 功能描述:MPU Xeon 制造商:Intel 功能描述:MPU Xeon? Processor 5120 RISC 64-Bit 65nm 1.86GHz 771-Pin LGA Box |

| BX805565130A S LAGC | 制造商:Intel 功能描述:5100 MEMORY CONTROLLER HUB CHIPSET |

| BX805565140P S LABN | 制造商:Intel 功能描述:MPU Xeon 制造商:Intel 功能描述:MPU Xeon? Processor 5140 RISC 64-Bit 65nm 2.33GHz 1.35V/1.5V 771-Pin FCLGA6 Box |

| BX805565148A S LABH | 制造商:Intel 功能描述:MPU Xeon |

| BX805565160A S L9RT | 制造商:Intel 功能描述:MPU Xeon? Processor 5160 RISC 64-Bit 65nm 3GHz 1.35V/1.5V 771-Pin FCLGA6 Box |

发布紧急采购,3分钟左右您将得到回复。