- 您现在的位置:买卖IC网 > PDF目录212189 > DDC118IRTCT (TEXAS INSTRUMENTS INC) 8-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PQCC48 PDF资料下载

参数资料

| 型号: | DDC118IRTCT |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | ADC |

| 英文描述: | 8-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PQCC48 |

| 封装: | GREEN, PLASTIC, QFN-48 |

| 文件页数: | 4/35页 |

| 文件大小: | 653K |

| 代理商: | DDC118IRTCT |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

DDC118

SBAS325B JUNE 2004 REVISED APRIL 2009

www.ti.com

12

DDC118 Frequency Response

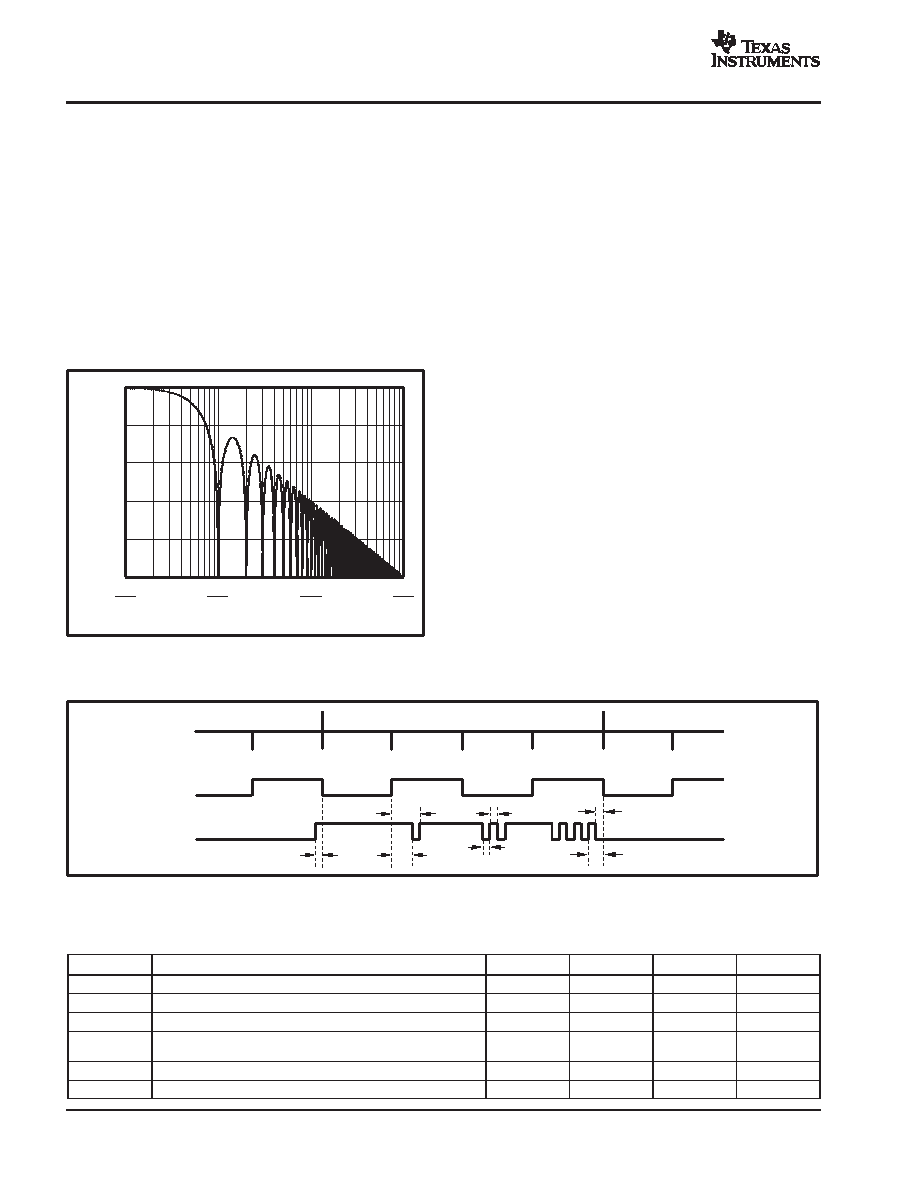

The frequency response of the DDC118 is set by the front

end integrators and is that of a traditional continuous time

integrator, as shown in Figure 7. By adjusting TINT, the

user can change the 3dB bandwidth and the location of the

notches in the response. The frequency response of the

Σ converter that follows the front end integrator is of no

consequence because the converter samples a held

signal from the integrators. That is, the input to the

Σ

converter is always a DC signal. Since the output of the

front end integrators are sampled, aliasing can occur.

Whenever the frequency of the input signal exceeds

one-half of the sampling rate, the signal will fold back down

to lower frequencies.

0

10

20

30

40

50

0.1

T

INT

100

T

INT

1

T

INT

10

T

INT

Frequency

Ga

in

(d

B

)

Figure 7. Frequency Response of the DDC118

Test Mode

When Test Mode is used, the inputs (IN1, IN2, IN3, IN4,

IN5, IN6, IN7, and IN8) are disconnected from the DDC118

integrators to enable the user to measure a zero input

signal regardless of the current supplied to the inputs. In

addition, packets of charge can be transferred to the

integrators in 11pC intervals to measure non-zero values.

The test mode works with both the continuous and

non-continuous modes. The timing diagram for the test

mode is shown in Figure 8 with the timing specifications

given in Table 2.

To enter Test Mode, hold TEST high while CONV

transitions. If TEST is held high during the entire

integration period, the integrators measure a zero value.

This mode can be used to help debug a design or perform

diagnostic tests. To apply packets of charge during Test

Mode, simply strobe TEST low then high before the next

CONV transition. Each rising edge of TEST causes

approximately 11pC of charge to be transferred to the

integrators. This charge transfer is independent of the

integration time. Data retrieval during Test Mode is

identical to normal operation. To exit Test Mode, take

TEST low and allow several cycles after exiting before

using the data.

t

1

t

3

t

4

t

4

t

6

t

5

t

2

Action

CONV

TEST

Integrate B

Integrate A

Test Mode Disabled

0pC into B

11pC into A

22pC into B

33pC into A

Test Mode Disabled

Test Mode Enabled: Inputs Disconnected

Integrate B

Integrate A

Figure 8. Timing Diagram of the Test Mode of the DDC118

Table 2. Timing for the DDC118 in the Test Mode

SYMBOL

DESCRIPTION

MIN

TYP

MAX

UNITS

t1

Setup Time for Test Mode Enable

100

ns

t2

Setup Time for Test Mode Disable

100

ns

t3

Hold Time for Test Mode Enable

100

ns

t4

From Rising Edge of TEST to the Edge of CONV while Test Mode

Enabled

1

s

t5

Falling Edge to Rising Edge of TEST

1

s

t6

Rising Edge to Falling Edge of TEST

1

s

相关PDF资料 |

PDF描述 |

|---|---|

| DPB25F0/25F | 50 CONTACT(S), FEMALE-FEMALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DPB25M/25M0 | 50 CONTACT(S), MALE-MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DPB25M/25M | 50 CONTACT(S), MALE-MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DPB25M0/25M0 | 50 CONTACT(S), MALE-MALE, D SUBMINIATURE CONNECTOR, SOLDER |

| DPB25M0/25M | 50 CONTACT(S), MALE-MALE, D SUBMINIATURE CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DDC118IRTCT | 制造商:Texas Instruments 功能描述:IC ADC 20BIT OCTAL 48-VQFN |

| DDC118IRTCT | 制造商:Texas Instruments 功能描述:A/D CONVERTER (A-D) IC ((NW)) |

| DDC118IRTCTG4 | 功能描述:模数转换器 - ADC Octal Current-Input 20-Bit RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| DDC11XEVM-PDK | 功能描述:数据转换 IC 开发工具 DDC11xEVM-PDK Eval Mod RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| DDC122LH | 制造商:DIODES 制造商全称:Diodes Incorporated 功能描述:NPN PRE-BIASED SMALL SIGNAL SOT-563 DUAL SURFACE MOUNT TRANSISTOR |

发布紧急采购,3分钟左右您将得到回复。