- 您现在的位置:买卖IC网 > PDF目录17120 > DK-DEV-2AGX125N (Altera)KIT DEV ARRIA II GX FPGA 2AGX125 PDF资料下载

参数资料

| 型号: | DK-DEV-2AGX125N |

| 厂商: | Altera |

| 文件页数: | 7/90页 |

| 文件大小: | 0K |

| 描述: | KIT DEV ARRIA II GX FPGA 2AGX125 |

| 产品培训模块: | Arria II GX FPGA Three Reasons to Use FPGA's in Industrial Designs |

| 特色产品: | Arria? II GX FPGA Development Kit |

| 标准包装: | 1 |

| 系列: | Arria II GX |

| 类型: | FPGA |

| 适用于相关产品: | EP2AGX125EF35 |

| 所含物品: | 板,线缆,CD,DVD,电源 |

| 产品目录页面: | 605 (CN2011-ZH PDF) |

| 相关产品: | 544-2599-5-ND - IC ARRIA II GX 125K 1152FBG 544-2598-5-ND - IC ARRIA II GX 125K 1152FBG 544-2597-5-ND - IC ARRIA II GX 125K 1152FBG |

| 其它名称: | 544-2600 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页

Chapter 1: Device Datasheet for Arria II Devices

1–7

Electrical Characteristics

December 2013

Altera Corporation

DC Characteristics

This section lists the supply current, I/O pin leakage current, on-chip termination

(OCT) accuracy and variation, input pin capacitance, internal weak pull-up and

pull-down resistance, hot socketing, and Schmitt trigger input specifications.

Supply Current

Standby current is the current the device draws after the device is configured with no

inputs or outputs toggling and no activity in the device. Because these currents vary

largely with the resources used, use the Microsoft Excel-based Early Power Estimator

(EPE) to get supply current estimates for your design.

f For more information about power estimation tools, refer to the PowerPlay Early Power

Estimator User Guide and the PowerPlay Power Analysis chapter.

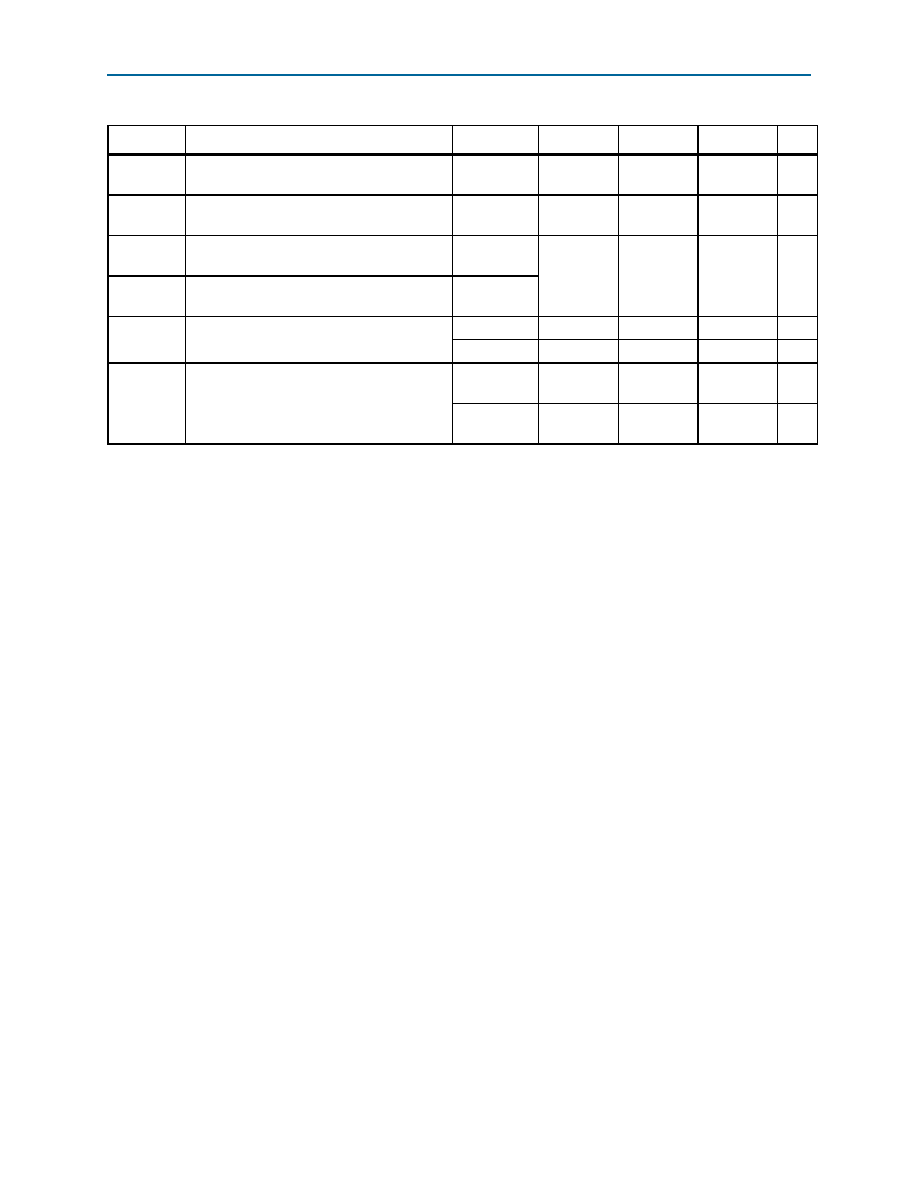

VCCL_GXBLn

Transceiver clock power (left side)

—

1.05

1.1

1.15

V

VCCL_GXBRn

Transceiver clock power (right side)

—

1.05

1.1

1.15

V

VCCH_GXBLn

Transmitter output buffer power (left side)

—

1.33/1.425

1.4/1.5 (5)

1.575

V

VCCH_GXBRn

Transmitter output buffer power (right side)

—

TJ

Operating junction temperature

Commercial

0

—

85

°C

Industrial

–40

—

100

°C

tRAMP

Power supply ramp time

Normal POR

(PORSEL=0)

0.05

—

100

ms

Fast POR

(PORSEL=1)

0.05

—

4

ms

Notes to Table 1–6:

(1) Altera recommends a 3.0-V nominal battery voltage when connecting VCCBAT to a battery for volatile key backup. If you do not use the volatile

security key, you may connect the VCCBAT to either GND or a 3.0-V power supply.

(2) VCCPD must be 2.5 V when VCCIO is 2.5, 1.8, 1.5, or 1.2 V. VCCPD must be 3.0 V when VCCIO is 3.0 V.

(3) n = 0, 1, or 2.

(4) VCCA_L/R must be connected to a 3.0-V supply if the clock multiplier unit (CMU) phase-locked loop (PLL), receiver clock data recovery (CDR), or

both, are configured at a base data rate > 4.25 Gbps. For data rates up to 4.25 Gbps, you can connect VCCA_L/R to either 3.0 V or 2.5 V.

(5) VCCH_GXBL/R must be connected to a 1.4-V supply if the transmitter channel data rate is > 6.5 Gbps. For data rates up to 6.5 Gbps, you can connect

VCCH_GXBL/R to either 1.4 V or 1.5 V.

(6) Transceiver power supplies do not have power-on-reset (POR) circuitry. After initial power-up, violating the transceiver power supply operating

conditions could lead to unpredictable link behavior.

Table 1–6. Recommended Operating Conditions for Arria II GZ Devices (Note 6) (Part 2 of 2)

Symbol

Description

Condition

Minimum

Typical

Maximum

Unit

相关PDF资料 |

PDF描述 |

|---|---|

| DK-V6-EMBD-G-J | DEV KIT EMBEDDED VIRTEX 6 |

| VE-J5V-EZ | CONVERTER MOD DC/DC 5.8V 25W |

| AP432AL-13 | IC VREF SHUNT PREC ADJ 8-SOP |

| GCC18DRTH-S13 | CONN EDGECARD 36POS .100 EXTEND |

| RCM15DRXS | CONN EDGECARD 30POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-2AGX260N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP2AGX260 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3C120N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3C120F780 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3CLS200N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3CLS200F780 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F152 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N/ES | 制造商:Altera Corporation 功能描述:KIT DEVELOPMENT STRATIX II ES |

发布紧急采购,3分钟左右您将得到回复。