- 您现在的位置:买卖IC网 > PDF目录17120 > DK-DEV-2AGX125N (Altera)KIT DEV ARRIA II GX FPGA 2AGX125 PDF资料下载

参数资料

| 型号: | DK-DEV-2AGX125N |

| 厂商: | Altera |

| 文件页数: | 8/90页 |

| 文件大小: | 0K |

| 描述: | KIT DEV ARRIA II GX FPGA 2AGX125 |

| 产品培训模块: | Arria II GX FPGA Three Reasons to Use FPGA's in Industrial Designs |

| 特色产品: | Arria? II GX FPGA Development Kit |

| 标准包装: | 1 |

| 系列: | Arria II GX |

| 类型: | FPGA |

| 适用于相关产品: | EP2AGX125EF35 |

| 所含物品: | 板,线缆,CD,DVD,电源 |

| 产品目录页面: | 605 (CN2011-ZH PDF) |

| 相关产品: | 544-2599-5-ND - IC ARRIA II GX 125K 1152FBG 544-2598-5-ND - IC ARRIA II GX 125K 1152FBG 544-2597-5-ND - IC ARRIA II GX 125K 1152FBG |

| 其它名称: | 544-2600 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页

1–8

Chapter 1: Device Datasheet for Arria II Devices

Electrical Characteristics

December 2013

Altera Corporation

I/O Pin Leakage Current

Table 1–7 lists the Arria II GX I/O pin leakage current specifications.

Table 1–8 lists the Arria II GZ I/O pin leakage current specifications.

Bus Hold

Bus hold retains the last valid logic state after the source driving it either enters the

high impedance state or is removed. Each I/O pin has an option to enable bus hold in

user mode. Bus hold is always disabled in configuration mode.

Table 1–9 lists bus hold specifications for Arria II GX devices.

Table 1–7. I/O Pin Leakage Current for Arria II GX Devices

Symbol

Description

Conditions

Min

Typ

Max

Unit

II

Input pin

VI = 0 V to VCCIOMAX

–10

—

10

A

IOZ

Tri-stated I/O pin

VO = 0 V to VCCIOMAX

–10

—

10

A

Table 1–8. I/O Pin Leakage Current for Arria II GZ Devices

Symbol

Description

Conditions

Min

Typ

Max

Unit

II

Input pin

VI = 0 V to VCCIOMAX

–20

—

20

A

IOZ

Tri-stated I/O pin

VO = 0 V to VCCIOMAX

–20

—

20

A

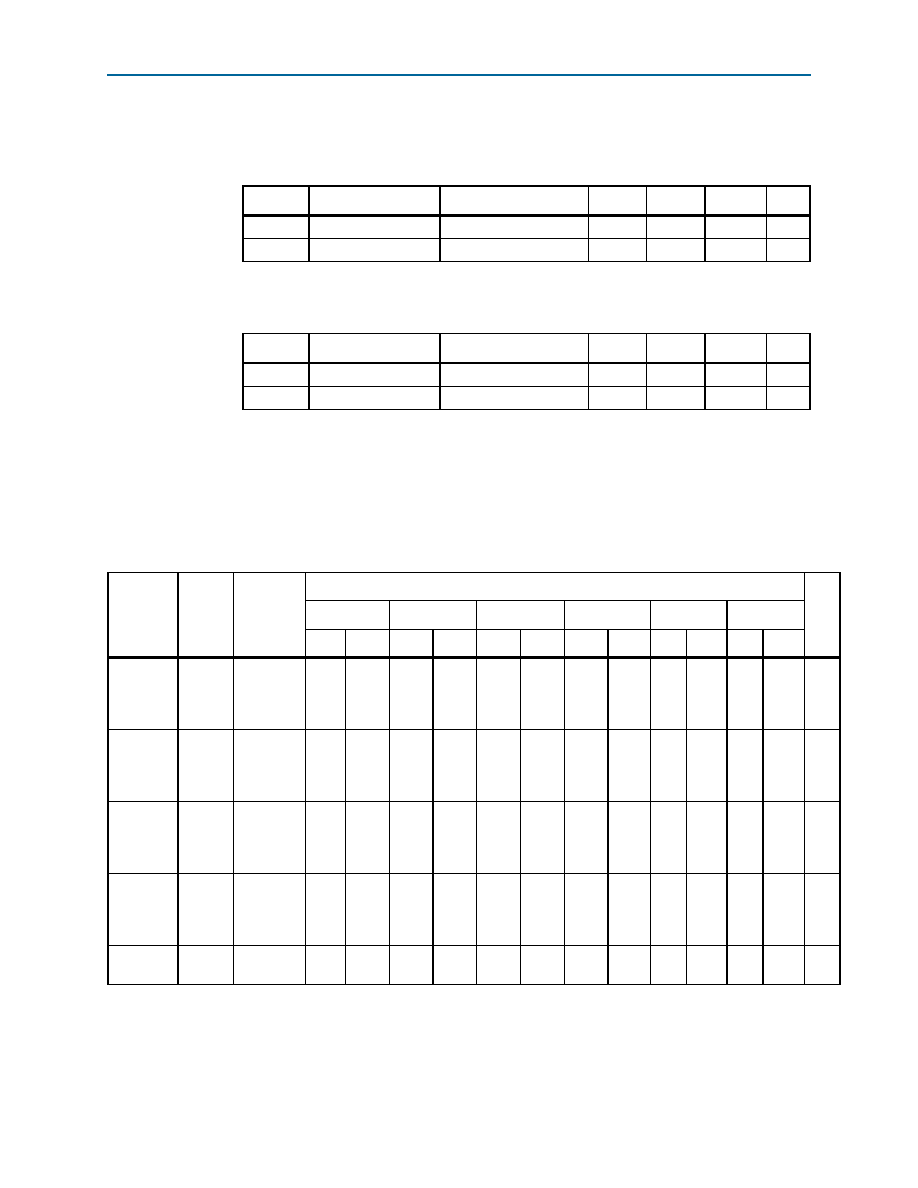

Table 1–9. Bus Hold Parameters for Arria II GX Devices (Note 1)

Parameter

Symbol

Cond.

VCCIO (V)

Unit

1.2

1.5

1.8

2.5

3.0

3.3

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Bus-hold

low,

sustaining

current

ISUSL

VIN > VIL

(max.)

8

—

12

—

30—50

—

70

—

70

—

A

Bus-hold

high,

sustaining

current

ISUSH

VIN < VIL

(min.)

–8

—

–12

—

–30

—

–50

—

–70

—

–70

—

A

Bus-hold

low,

overdrive

current

IODL

0V <VIN <

VCCIO

—

125

—

175

—

200

—

300

—

500

—

500

A

Bus-hold

high,

overdrive

current

IODH

0V <VIN <

VCCIO

—

–125

—

–175

—

–200

—

–300

—

–500

—

–500

A

Bus-hold

trip point

VTRIP

—

0.3

0.9

0.375

1.125

0.68

1.07

0.7

1.7

0.8

2

0.8

2

V

Note to Table 1–9:

(1) The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

相关PDF资料 |

PDF描述 |

|---|---|

| DK-V6-EMBD-G-J | DEV KIT EMBEDDED VIRTEX 6 |

| VE-J5V-EZ | CONVERTER MOD DC/DC 5.8V 25W |

| AP432AL-13 | IC VREF SHUNT PREC ADJ 8-SOP |

| GCC18DRTH-S13 | CONN EDGECARD 36POS .100 EXTEND |

| RCM15DRXS | CONN EDGECARD 30POS DIP .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DK-DEV-2AGX260N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP2AGX260 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3C120N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3C120F780 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3CLS200N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3CLS200F780 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N | 功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP3SL150F152 RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| DK-DEV-3SL150N/ES | 制造商:Altera Corporation 功能描述:KIT DEVELOPMENT STRATIX II ES |

发布紧急采购,3分钟左右您将得到回复。