- 您现在的位置:买卖IC网 > PDF目录1915 > DS3141+ (Maxim Integrated Products)IC FRAMER DS3/E3 SNGL 144CSBGA PDF资料下载

参数资料

| 型号: | DS3141+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 17/88页 |

| 文件大小: | 0K |

| 描述: | IC FRAMER DS3/E3 SNGL 144CSBGA |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 160 |

| 控制器类型: | DS3/E3 调帧器 |

| 接口: | LIU |

| 电源电压: | 3.135 V ~ 3.465 V |

| 电流 - 电源: | 80mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA,CSPBGA |

| 供应商设备封装: | 144-TECSBGA(13x13) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

DS3141/DS3142/DS3143/DS3144 Single/Dual/Triple/Quad DS3/E3 Framers

24 of 88

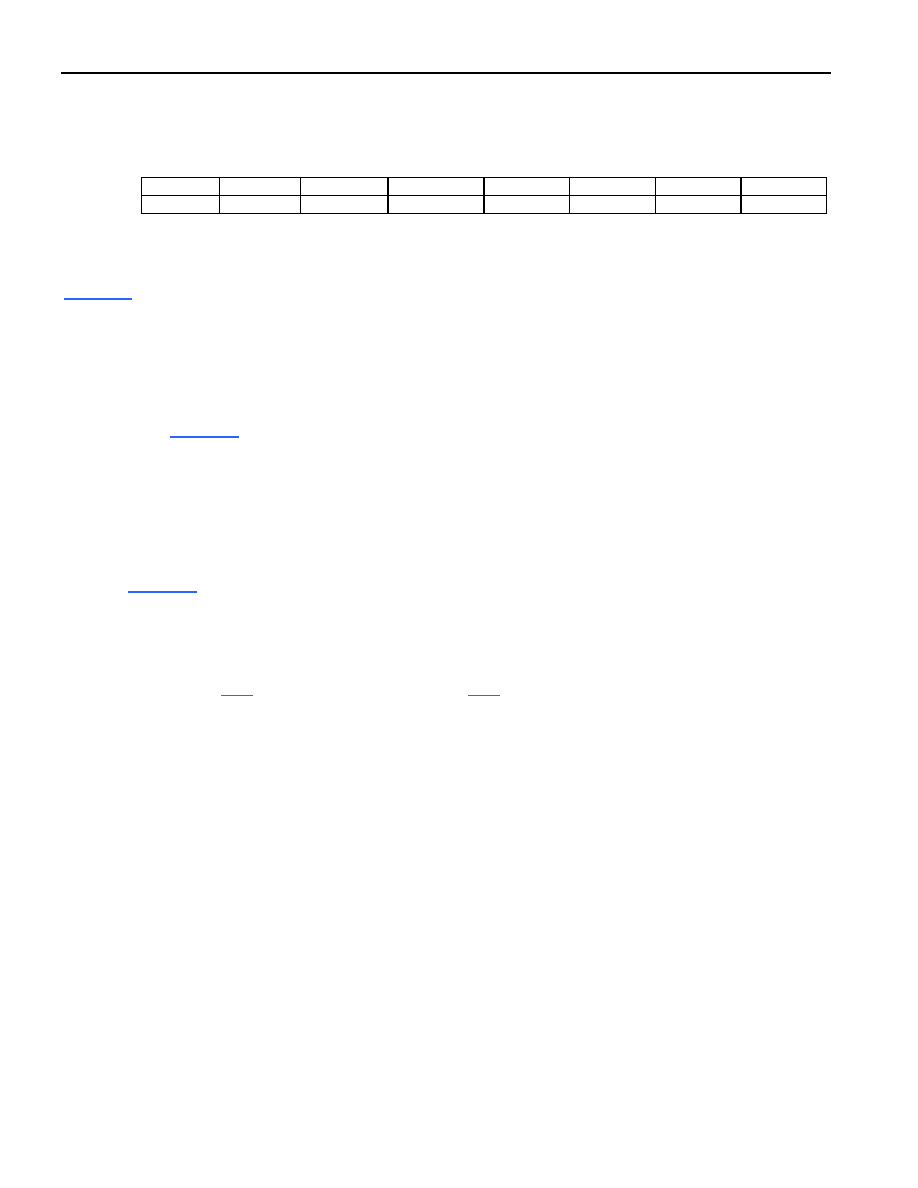

Register Name:

MC2

Register Description:

Master Configuration Register 2

Register Address:

02h

Bit #

7

6

5

4

3

2

1

0

Name

OSTCS

TCCLK

N/A

DLB

LLB

PLB

Default

0

—

0

Bit 0: Payload Loopback Enable (PLB). When payload loopback is enabled, the transmit formatter operates from

the receive clock (rather than TICLK) and sources DS3/E3 payload bits from the receive data stream rather than

from the TDAT input pin. Receive data is still available on the RDAT output pin during payload loopback. See

Figure 1-1 for a visual description of this loopback.

0 = disable payload loopback

1 = enable payload loopback

Bit 1: Line Loopback Enable (LLB). Line loopback connects the TPOS, TNEG, and TCLK output pins to the

RPOS, RNEG, and RCLK input pins. When line loopback is enabled, the receive framer continues to process the

incoming receive data stream and present it on the RDAT pin; the output of the transmit formatter is ignored. Line

loopback and diagnostic loopback can be active at the same time to support simultaneous local and far-end

loopbacks. See Figure 1-1 for a visual description of this loopback.

0 = disable line loopback

1 = enable line loopback

Bit 2: Diagnostic Loopback Enable (DLB). When diagnostic loopback is enabled, the receive framer sources

data from the transmit formatter rather than the RCLK, RPOS, and RNEG input pins. Transmit data is sourced prior

to transmit AIS generation, unframed all-ones generation, TCLK/TPOS/TNEG pin inversion, and TPOS/TNEG

force-high logic. This allows the device to transmit AIS or unframed all ones to the far end while locally looping

back the actual transmit data stream, which could be test patterns or other traffic that should not be sent to the far

end. See Figure 1-1 for a visual description of this loopback.

0 = disable diagnostic loopback

1 = enable diagnostic loopback

Bit 6: Transmit Constant Clock Select (TCCLK). When TCCLK is set to logic 1, the device outputs a constant

transmit clock on the TDEN/TGCLK pin instead of a data enable or gapped clock. This bit has precedence over the

0 = the function of the TDEN/TGCLK pin is controlled by TDENMS control bit

1 = the TDEN/TGCLK pin is a constant transmit clock output

Bit 7: One-Second Timer Clock Select (OSTCS). This control bit selects the clock source for the internal one-

second timer.

0 = use RCLK

1 = use TICLK

相关PDF资料 |

PDF描述 |

|---|---|

| DS31412N | IC 12CH DS3/3 FRAMER 349-BGA |

| DS3150TN | IC LIU T3/E3/STS-1 IND 48-TQFP |

| DS3154N+ | IC LIU DS3/E3/STS-1 QD 144CSBGA |

| DS3164+ | IC ATM/PACKET PHY QUAD 400-BGA |

| DS3170+ | IC TXRX DS3/E3 100-CSBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| DS3141+ | 功能描述:网络控制器与处理器 IC Single DS3/E3 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS314-1010NR WAF | 制造商:ON Semiconductor 功能描述: |

| DS31412 | 功能描述:网络控制器与处理器 IC 12 Port DS3/E3 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS31412N | 功能描述:网络控制器与处理器 IC 12 Port DS3/E3 Framer RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| DS31415 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:3-Input, 4-Output, Single DPLL Timing IC with Sub-ps Output Jitter and 1588 Clock |

发布紧急采购,3分钟左右您将得到回复。