- 您现在的位置:买卖IC网 > PDF目录16871 > EVAL-AD5560EBUZ (Analog Devices Inc)BOARD EVALUATION FOR AD5560 PDF资料下载

参数资料

| 型号: | EVAL-AD5560EBUZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 35/68页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD5560 |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电源监控器/跟踪器/序列发生器 |

| 已用 IC / 零件: | AD5560 |

| 次要属性: | 串行接口 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

AD5560

Data Sheet

Rev. D | Page 40 of 68

The transfer function for these 16-bit DACs is

DUTGND

CODE

DAC

OFFSET

V

CODE

DAC

V

VCLL

VCLH

REF

+

×

×

=

16

2

_

125

.

5

2

125

.

5

,

The transfer function for the clamp current value is

GAIN

AMP

MI

R

CODE

DAC

V

ICLH

ICLL

SENSE

REF

_

2

32768

125

.

5

,

16

×

×

=

where:

RSENSE is the sense resistor.

MI_AMP_GAIN is the gain of the MI amp (either 10 or 20).

OSD DAC

The OSD DAC is a 16-bit DAC function, again a resistor string

DAC guaranteeing monotonicity. The 16-bit binary digital

code loaded to the DAC register determines at what node on

the string the voltage is tapped off before being fed to the

output amplifier. The OSD function is used to program the

voltage difference needed between the force and sense lines

before the alarm circuit flags an error. The OSD DAC has a

range of 0.62 V to 5 V. The transfer function is as follows:

×

=

16

2

CODE

DAC

VREF

V

OUT

(1)

The offset DAC does not affect the OSD DAC output range.

DUTGND DAC

Similarly, the DUTGND DAC (DGS) is a 16-bit DAC and uses

a resistor string DAC to guarantee monotonicity. The 16-bit

binary digital code loaded to the DAC register determines at

what node on the string the voltage is tapped off before being

fed to the output amplifier. This function is used to program

the voltage difference needed between the DUTGND and

AGND lines before the alarm circuit flags an error.

The DUTGND DAC has a range of 0 V to 5 V. The transfer

function for this 16-bit DAC is shown in Equation 1.

The offset DAC does not affect the OSD DAC output range.

OFFSET DAC

In addition to the offset and gain trim, there is also a 16-bit

offset DAC that offsets the output of each DAC on chip. There-

fore, depending on headroom available, the input to the force

amplifier can be arranged either symmetrically or asymmetrically

about DUTGND but always within a voltage span of 25 V. Some

extra gain is included to allow for system error correction using

the m (gain) and c (offset) registers.

The usable voltage range is 22 V to +25 V. Full scale loaded

to the offset DAC does not give a useful output voltage range

because the output amplifiers are limited by available footroom.

Table 15 shows the effect of the offset DAC on other DACs in

the device (clamp, comparator, and force DACs).

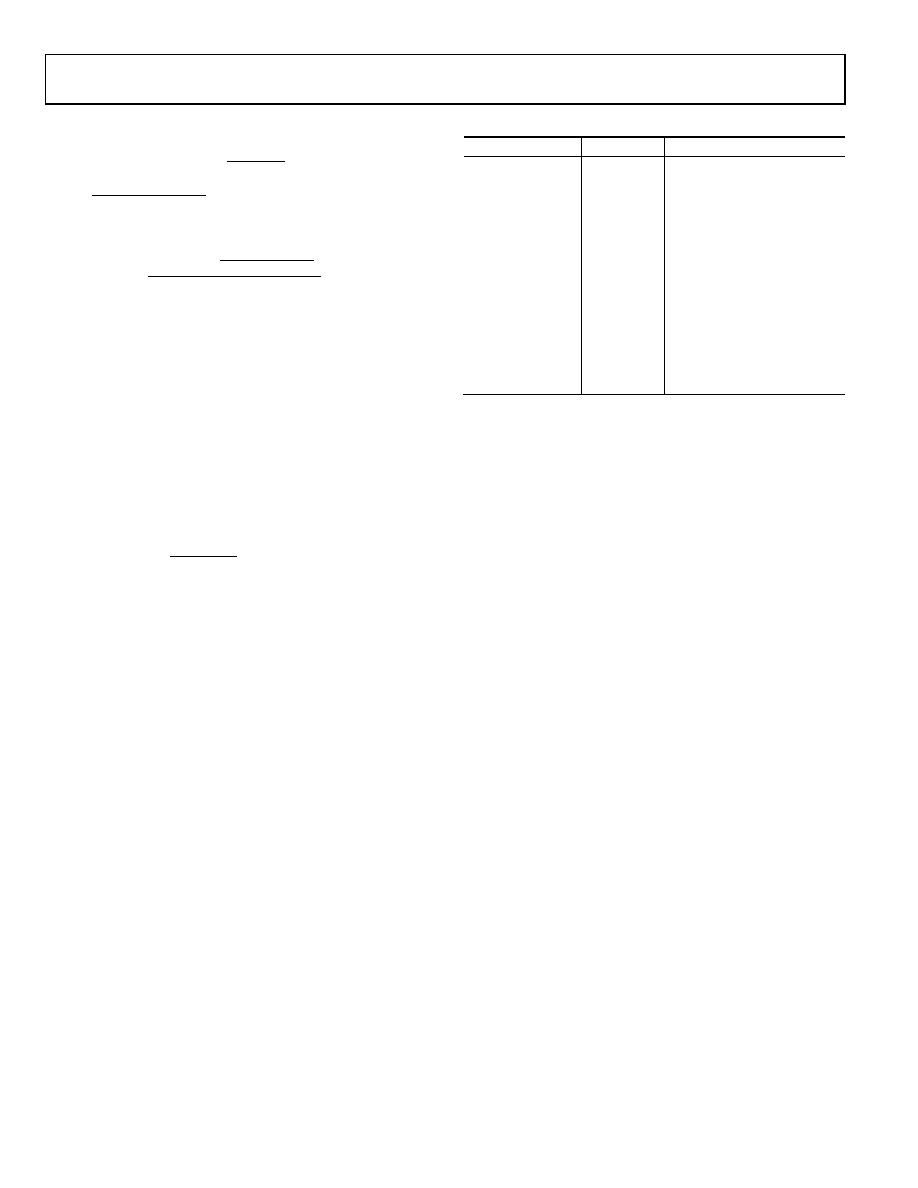

Table 15. Offset DAC Relationship with Other DACs, VREF = 5 V

Offset DAC Code

DAC Code1

DAC Output Voltage Range

0

0.00

0

32,768

12.81

0

65,535

25.62

…

32,768

0

12.81

32,768

0.00

32,768

65,535

12.81

…

57,344

0

22.42

57,344

32,768

9.61

57,344

65,535

3.20

…

65,355

…

Footroom limitations

1 DAC code shown for 16-bit force DAC.

OFFSET AND GAIN REGISTERS

Each DAC level contains independent offset and gain control

registers that allow the user to digitally trim offset and gain.

These registers give the user the ability to calibrate out errors

in the complete signal chain (including the DAC) using the

internal m and c registers, which hold the correction factors.

The digital input transfer function for the DACs can be

represented as

x2 = [x1 × (m + 1)/2n] + (c – 2n – 1)

where:

x2 is the data-word loaded to the resistor string DAC.

x1 is the 16-bit data-word written to the DAC input register.

m is the code in the gain register (default code = 216 – 1).

n is the DAC resolution (n = 16).

c is the code in the offset register (default code = 215).

Offset and Gain Registers for the Force Amplifier DAC

The force amplifier input (FIN) DAC level contains independent

offset and gain control registers that allow the user to digitally

trim offset and gain. There is one set of registers for the force

voltage range: x1, m, and c.

Offset and Gain Registers for the Comparator DACs

The comparator DAC levels contain independent offset and

gain control registers that allow the user to digitally trim offset

and gain. There are seven sets of registers consisting of a combi-

nation of x1, m, and c, one set each for the five internal force

current ranges and one set each for the two external high

current ranges.

Offset and Gain Registers for the Clamp DACs

The clamp DAC levels contain independent offset and gain

control registers that allow the user to digitally trim offset

and gain. One set of registers covers the VSENSE range, the five

internal force current ranges, and the two external high current

ranges. Both clamp DAC x1 registers and their associated offset

and gain registers are 16 bit.

相关PDF资料 |

PDF描述 |

|---|---|

| EVAL-AD5522EBDZ | BOARD EVAL FOR 14X14MM AD5522 |

| EVAL-AD5520EBZ | BOARD EVAL FOR AD5520 |

| MAX6198AESA+T | IC VREF SERIES PREC 4.096V 8SOIC |

| QPI-5-EVAL1 | EVALUATION BOARD FOR QPI-5 |

| H6MMH-4006M | DIP CABLE - HDM40H/AE40M/HDM40H |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD5570EB | 制造商:Analog Devices 功能描述:DEV TOOLS, TRUE ACCURACY, 16BIT 12V/ 15V, SERL INPUT VOLT O - Bulk |

| EVAL-AD5570EBZ | 功能描述:BOARD EVALUATION FOR AD5570 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5570SDZ | 功能描述:BOARD EVAL FOR AD5570 RoHS:是 类别:编程器,开发系统 >> 评估板 - 数模转换器 (DAC) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- DAC 的数量:4 位数:12 采样率(每秒):- 数据接口:串行,SPI? 设置时间:3µs DAC 型:电流/电压 工作温度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| EVAL-AD5590EBZ | 功能描述:BOARD EVAL FOR AD5590 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD5620EB | 制造商:AD 制造商全称:Analog Devices 功能描述:Single, 12-/14-/16-Bit nanoDAC with 5 ppm/C On-Chip Reference in SOT-23 |

发布紧急采购,3分钟左右您将得到回复。