- 您现在的位置:买卖IC网 > PDF目录16594 > EVAL-AD7195EBZ (Analog Devices Inc)BOARD EVAL FOR AD7195 PDF资料下载

参数资料

| 型号: | EVAL-AD7195EBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 43/45页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD7195 |

| 设计资源: | EVAL-AD7195EBZ Schematic AD7195 Gerber Files |

| 标准包装: | 1 |

| 主要目的: | 接口,模拟前端(AFE) |

| 已用 IC / 零件: | AD7195 |

| 次要属性: | 图形用户界面,USB 接口 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页当前第43页第44页第45页

AD7195

Rev. 0 | Page 6 of 44

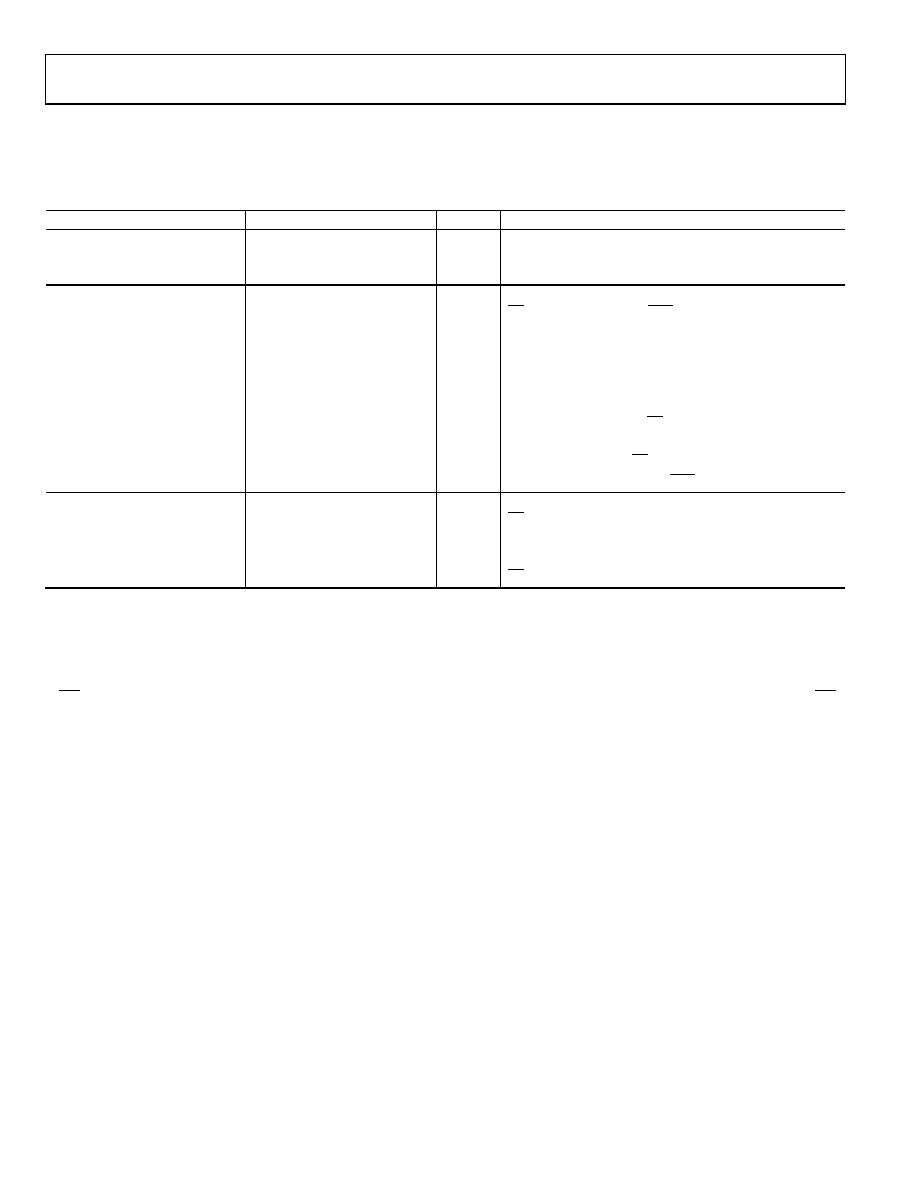

TIMING CHARACTERISTICS

AVDD = 4.75 V to 5.25 V, DVDD = 2.7 V to 5.25 V, AGND = DGND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = DVDD, unless

otherwise noted.

Table 2.

Parameter

Limit at TMIN, TMAX (B Version)

Unit

Conditions/Comments1, 2

READ AND WRITE OPERATIONS

t3

100

ns min

SCLK high pulse width

t4

100

ns min

SCLK low pulse width

READ OPERATION

t1

0

ns min

CS falling edge to DOUT/RDY active time

60

ns max

DVDD = 4.75 V to 5.25 V

80

ns max

DVDD = 2.7 V to 3.6 V

t23

0

ns min

SCLK active edge to data valid delay4

60

ns max

DVDD = 4.75 V to 5.25 V

80

ns max

DVDD = 2.7 V to 3.6 V

t55, 6

10

ns min

Bus relinquish time after CS inactive edge

80

ns max

t6

0

ns min

SCLK inactive edge to CS inactive edge

t7

10

ns min

SCLK inactive edge to DOUT/RDY high

WRITE OPERATION

t8

0

ns min

CS falling edge to SCLK active edge setup time4

t9

30

ns min

Data valid to SCLK edge setup time

t10

25

ns min

Data valid to SCLK edge hold time

t11

0

ns min

CS rising edge to SCLK edge hold time

1 Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of DVDD) and timed from a voltage level of 1.6 V.

2 See Figure 3 and Figure 4.

3 These numbers are measured with the load circuit shown in Figure 2 and defined as the time required for the output to cross the VOL or VOH limits.

4 The SCLK active edge is the falling edge of SCLK.

5 These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit shown in Figure 2. The measured number

is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the

true bus relinquish times of the part and, as such, are independent of external bus loading capacitances.

6

RDY returns high after a read of the data register. In single conversion mode and continuous conversion mode, the same data can be read again, if required, while RDY

is high, although care should be taken to ensure that subsequent reads do not occur close to the next output update. If the continuous read feature is enabled, the

digital word can be read only once.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B6B-EX | CONVERTER MOD DC/DC 95V 75W |

| ECM18DRPI | CONN EDGECARD 36POS DIP .156 SLD |

| EEM25DRMT | CONN EDGECARD 50POS .156 WW |

| V24C8C100BG3 | CONVERTER MOD DC/DC 8V 100W |

| H1WXH-2636G | IDC CABLE - HPL26H/AE26G/X |

相关代理商/技术参数 |

参数描述 |

|---|---|

| EVAL-AD7262EDZ | 功能描述:BOARD EVAL CONTROL AD7262 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7264EDZ | 功能描述:BOARD EVALUATION FOR AD7264 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

| EVAL-AD7265CB | 制造商:AD 制造商全称:Analog Devices 功能描述:Differential/Single-Ended Input, Dual 1 MSPS, 12-Bit, 3-Channel SAR ADC |

| EVAL-AD7265CB1 | 制造商:AD 制造商全称:Analog Devices 功能描述:Differential Input, Dual 1 MSPS, 12-Bit, 3-Channel SAR ADC |

| EVAL-AD7265EDZ | 功能描述:BOARD EVAL FOR AD7265 A/D CONV RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件 |

发布紧急采购,3分钟左右您将得到回复。