- 您现在的位置:买卖IC网 > PDF目录67593 > FX980L6 (CML MICROSYSTEMS PLC) SPECIALTY CONSUMER CIRCUIT, PQCC44 PDF资料下载

参数资料

| 型号: | FX980L6 |

| 厂商: | CML MICROSYSTEMS PLC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 38/86页 |

| 文件大小: | 821K |

| 代理商: | FX980L6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

TETRA Baseband Processor

FX980

1997 Consumer Microcircuits Limited

43

D/980/3

RxErrorStatus

Title:

Receive Error Status register.

Address:

$0x20

Function:

R

Description:

This register is the Rx Data path error status register. The RxIrqActive bit is set active when one

of the other bits in this register is the source of an interrupt event. All these error conditions are

caused by transitory events, therefore the error condition is latched (marked with an ‘L’).

Reading this status register causes all latched bits to be set inactive unless an error event is

currently pending.

Setting any bit of this register High will cause an interrupt to be generated (N_IRQ will be set

Low) if the source of the interrupt has not been masked in the corresponding Mask register.

Bit

Name

Active State

Function

7

RxDataPathQOF

High

RL

Data path gain, phase and offset (GPO) adjustment unit: Q

channel overflow error status bit.

6

RxDataPathIOF

High

RL

Data path gain, phase and offset (GPO) adjustment unit:

I channel overflow error status bit.

5

AdcQOF

High

RL

ADC Q channel overflow error due to excessive input

amplitude.

4

AdcIOF

High

RL

ADC I channel overflow error due to excessive input

amplitude.

3

Rx63tapOF

High

RL

63-tap I and Q filter data accumulator overflow error status

bit.

2

Rx49tapOF

High

RL

49-tap I and Q filter data accumulator overflow error status

bit.

1

EvenSamplePhase

High

RL

When this status bit is active, the associated interrupt may

be used to re-synchronise the Rx data if for any reason

data synchronisation is lost. If the corresponding mask bit

is set inactive, an interrupt will be generated on the next

Q-phase data in the Rx output register. The next falling

edge of SClk with RxFS High indicates the LSB of the Q

channel data. The mask bit should be disabled after this to

prevent continuous Q-phase interrupts.

0

RxIrqActive

High

RL

This bit is set High if there is an active interrupt caused by

one of the status bits in this register.

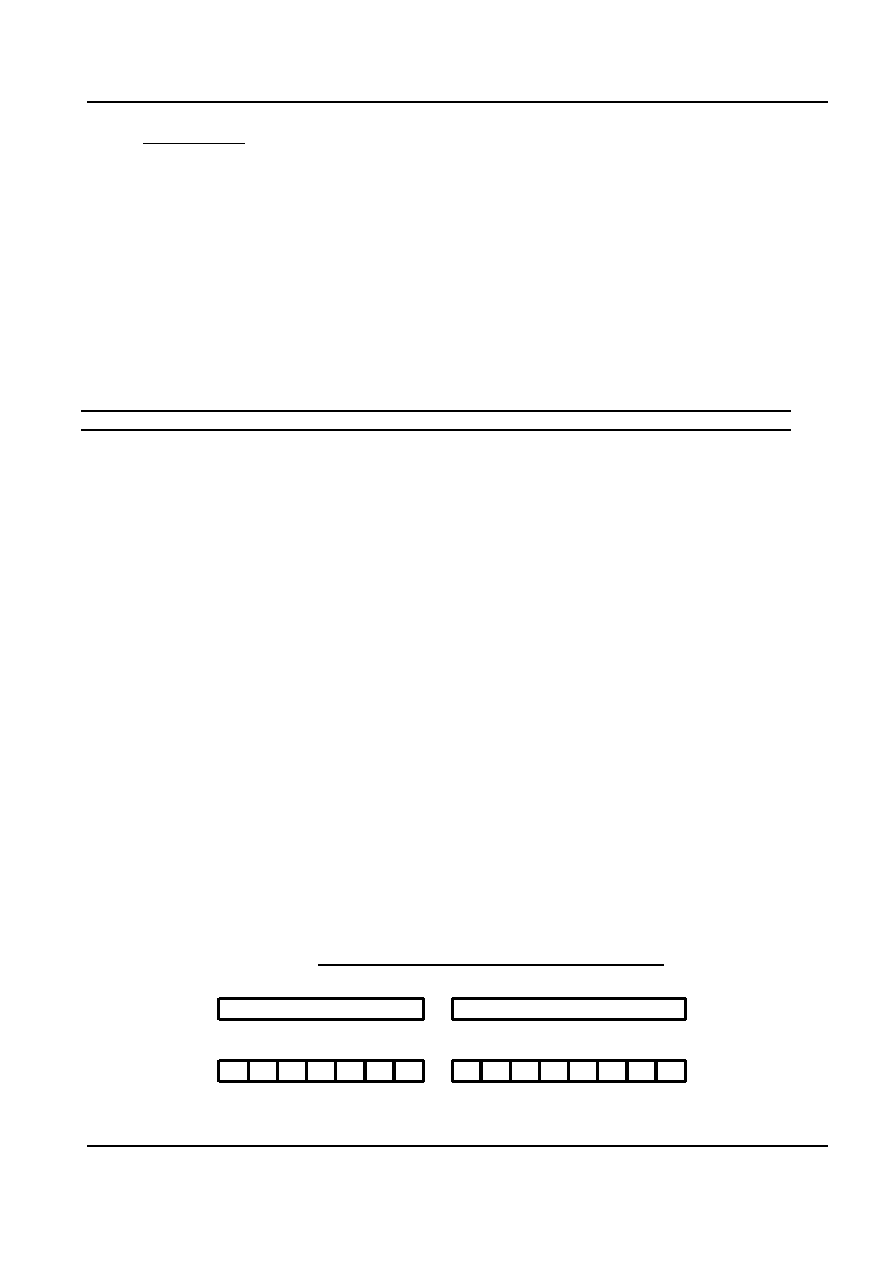

Address and Data format for RxErrorStatus access

D1 D0

D7 D6 D5 D4 D3 D2

Data field [7:0]

Address field [6:0]

0

1

0

相关PDF资料 |

PDF描述 |

|---|---|

| FXO-HC320-0.7500M | CRYSTAL OSCILLATOR, CLOCK, 0.75 MHz, HCMOS OUTPUT |

| FXO-HC320-180.00M | CRYSTAL OSCILLATOR, CLOCK, 180 MHz, HCMOS OUTPUT |

| FXO-HC325-180.00M | CRYSTAL OSCILLATOR, CLOCK, 180 MHz, HCMOS OUTPUT |

| FXO-HC325R-106.25M | CRYSTAL OSCILLATOR, CLOCK, 106.25 MHz, HCMOS OUTPUT |

| FXO-HC320R-106.25M | CRYSTAL OSCILLATOR, CLOCK, 106.25 MHz, HCMOS OUTPUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| FX981006 | 制造商:Thomas & Betts 功能描述: |

| FX-991ES | 制造商:CASIO 功能描述:CALCULATOR |

| FX-991ES+ | 制造商:CASIO 功能描述:CALCULATOR ((NS)) |

| FX992S | 制造商:CASIO 功能描述:CALCULATOR SCIENTIFIC 制造商:CASIO 功能描述:CALCULATOR, SCIENTIFIC |

| FX996 | 制造商:BACO Controls Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。