- 您现在的位置:买卖IC网 > PDF目录67593 > FX980L6 (CML MICROSYSTEMS PLC) SPECIALTY CONSUMER CIRCUIT, PQCC44 PDF资料下载

参数资料

| 型号: | FX980L6 |

| 厂商: | CML MICROSYSTEMS PLC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 4/86页 |

| 文件大小: | 821K |

| 代理商: | FX980L6 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

TETRA Baseband Processor

FX980

1997 Consumer Microcircuits Limited

12

D/980/3

1.5.6.2 Command Read Interface

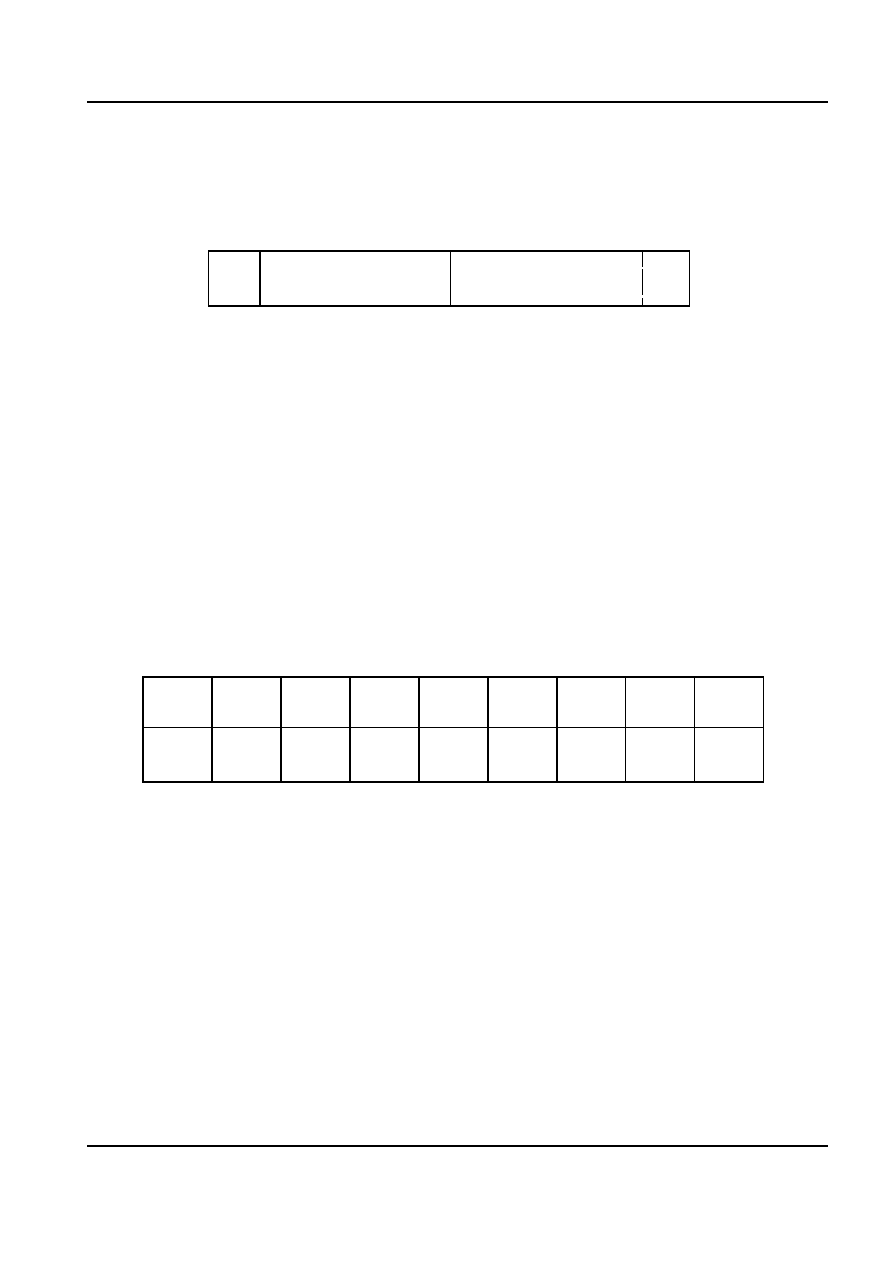

Command read data is either output on one of the serial read ports, or driven out in the last 8 bits

(data field) on the Cmd port. When command read data is output on a serial read port, the read

address is put in the most significant half of the word, and the read data in the least significant half.

MSB

LSB

0

Read Address

Data

15

14

8

7

0

Command Read Serial Word

1.5.6.3 Rx Data Interface

The Rx Data interface is used only for output of the I and Q received data, unless it is operating in the

mode where CmdRd data is directed to it. When data reception is enabled, I and Q received data will

be output at either 8x or 4x the symbol rate, under control of command register RxSetup2. (see

Section 1.5.7). This is achieved by reducing the serial interface clock rate from MCLK/2 to MCLK/4

and discarding alternate data samples under control of command registers ConfigCtrl1 and

RxSetup2. 16-bit I and Q data words are output at the Rx Data interface, I data and MSB first (by

default), on the rising edge of SClk.

1.5.6.4 Transmission of Data

The address of the Tx FIFO is given consecutive locations ($0x04-$0x07), which allows the address

bits A1 and A0 (bits 11 and 10) of the Command Transmit Data Serial Word to be utilised as transmit

control functions. Data to be transmitted can be in either one or four (2-bit) symbol blocks, which are

subsequently modulated into the DQPSK constellation, or in 3-bit words, which map directly into

constellation points according to the table shown below.

3 bit

code

000

001

010

011

100

101

110

111

I

Q

1

0

0.7071

0

1

-0.7071

0.7071

-1

0

-0.7071

0

-1

0.7071

-0.7071

Constellation map

The user initiates a transmit frame by asserting the TxEn bit in the TxSetup register.

However,

internal transmission of the data will wait until specific conditions have been met. Firstly, a valid data

word must be written into the FIFO with the TxRampEn bit of the TxSetup register asserted.

Secondly, the internal symbol clock must be active.

Therefore there is a variable delay between

asserting the TxEn bit and transmission starting.

The user may poll the TxPathEn bit of the

TxFIFOStatus register to establish when transmission has started, and in this case the active state of

TxPathEn in High. In general, the user will wish to know when the transmit frame has completed.

This is indicated by TxPathEn returning Low.

To relieve the user of polling overheads when waiting for Tx frame completion, an interrupt can be set

up to occur on the transition of the TxPathEn bit from High to Low.

In such circumstances, the

interrupt activation state of the TxPathEn can be considered Low.

相关PDF资料 |

PDF描述 |

|---|---|

| FXO-HC320-0.7500M | CRYSTAL OSCILLATOR, CLOCK, 0.75 MHz, HCMOS OUTPUT |

| FXO-HC320-180.00M | CRYSTAL OSCILLATOR, CLOCK, 180 MHz, HCMOS OUTPUT |

| FXO-HC325-180.00M | CRYSTAL OSCILLATOR, CLOCK, 180 MHz, HCMOS OUTPUT |

| FXO-HC325R-106.25M | CRYSTAL OSCILLATOR, CLOCK, 106.25 MHz, HCMOS OUTPUT |

| FXO-HC320R-106.25M | CRYSTAL OSCILLATOR, CLOCK, 106.25 MHz, HCMOS OUTPUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| FX981006 | 制造商:Thomas & Betts 功能描述: |

| FX-991ES | 制造商:CASIO 功能描述:CALCULATOR |

| FX-991ES+ | 制造商:CASIO 功能描述:CALCULATOR ((NS)) |

| FX992S | 制造商:CASIO 功能描述:CALCULATOR SCIENTIFIC 制造商:CASIO 功能描述:CALCULATOR, SCIENTIFIC |

| FX996 | 制造商:BACO Controls Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。