- 您现在的位置:买卖IC网 > PDF目录223993 > HY5DU56422ALF-J (HYNIX SEMICONDUCTOR INC) 64M X 4 DDR DRAM, 0.7 ns, PBGA60 PDF资料下载

参数资料

| 型号: | HY5DU56422ALF-J |

| 厂商: | HYNIX SEMICONDUCTOR INC |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, 0.7 ns, PBGA60 |

| 封装: | FBGA-60 |

| 文件页数: | 11/36页 |

| 文件大小: | 395K |

| 代理商: | HY5DU56422ALF-J |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

Rev. 0.1/Apr. 02

19

HY5DU56422A(L)F

HY5DU56822A(L)F

HY5DU561622A(L)F

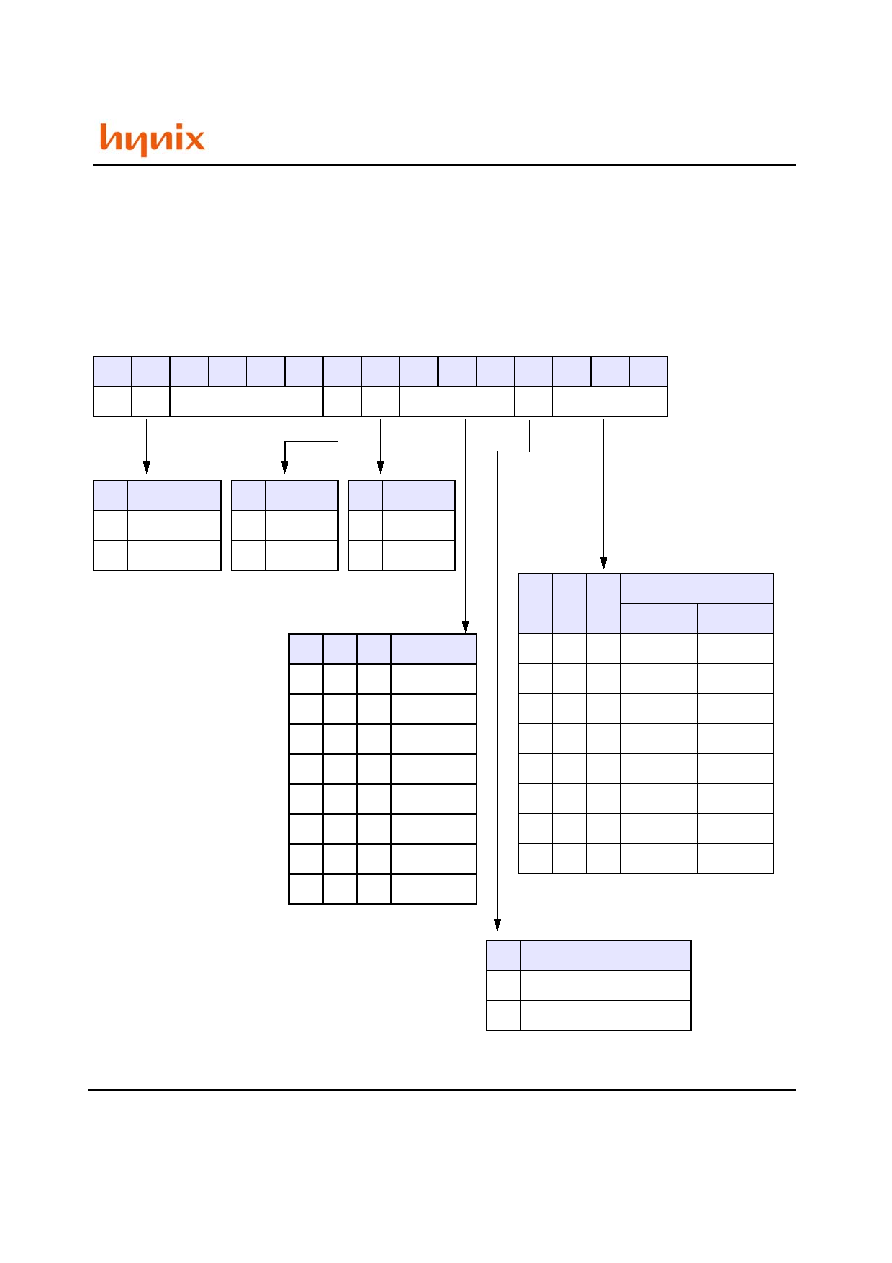

MODE REGISTER SET (MRS)

The mode register is used to store the various operating modes such as /CAS latency, addressing mode, burst length,

burst type, test mode, DLL reset. The mode register is programed via MRS command. This command is issued by the

low signals of /RAS, /CAS, /CS, /WE and BA0. This command can be issued only when all banks are in idle state and

CKE must be high at least one cycle before the Mode Register Set Command can be issued. Two cycles are required to

write the data in mode register. During the MRS cycle, any command cannot be issued. Once mode register field is

determined, the information will be held until resetted by another MRS command.

BA1

BA0

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

0

RFU

DR

TM

CAS Latency

BT

Burst Length

A2

A1

A0

Burst Length

Sequential

Interleave

0

Reserved

001

2

010

4

011

8

1

0

Reserved

1

0

1

Reserved

1

0

Reserved

1

Reserved

A3

Burst Type

0

Sequential

1Interleave

A6

A5

A4

CAS Latency

000

Reserved

001

Reserved

010

2

011

3

100

Reserved

101

1.5

110

2.5

111

Reserved

A7

Test Mode

0Normal

1

Test

A8

DLL Reset

0No

1Yes

BA0

MRS Type

0MRS

1EMRS

相关PDF资料 |

PDF描述 |

|---|---|

| HY5MS5B6LF-H | 16M X 16 DDR DRAM, 6.5 ns, PBGA60 |

| HY5PS1G831ALFP-C4 | 128M X 8 DDR DRAM, PBGA68 |

| HY5PS1G831ALFP-Y5 | 128M X 8 DDR DRAM, PBGA68 |

| HY5RS573225AFP-16L | 8M X 32 DDR DRAM, 0.28 ns, PBGA136 |

| HY5V28CF-S | 16M X 8 SYNCHRONOUS DRAM, 6 ns, PBGA54 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| HY5DU56422ALT | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64Mx4|2.5V|8K|J/M/K/H/L|DDR SDRAM - 256M |

| HY5DU56422ALT-H | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256M-S DDR SDRAM |

| HY5DU56422ALT-J | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256M-S DDR SDRAM |

| HY5DU56422ALT-K | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256M-S DDR SDRAM |

| HY5DU56422ALT-L | 制造商:HYNIX 制造商全称:Hynix Semiconductor 功能描述:256M-S DDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。