- 您现在的位置:买卖IC网 > PDF目录67711 > IDT49C465PQF8 (INTEGRATED DEVICE TECHNOLOGY INC) 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 PDF资料下载

参数资料

| 型号: | IDT49C465PQF8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 算术逻辑单元 |

| 英文描述: | 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 |

| 封装: | PLASTIC, QFP-144 |

| 文件页数: | 35/39页 |

| 文件大小: | 299K |

| 代理商: | IDT49C465PQF8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页

5

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

COMMERCIAL TEMPERATURE RANGE

SD

M D

ED C

CBI

CBO

MEMOR Y

I/O

CPU

I/O

CHEC KBITS

EXT. BUFFER

MD

EDC

CBI

CBO

MEMORY

IN PU T BU S

C HEC KBIT

I/O

MEMORY

OUTPUT BUS

CPU BUS

SD

EXT. BU FFER

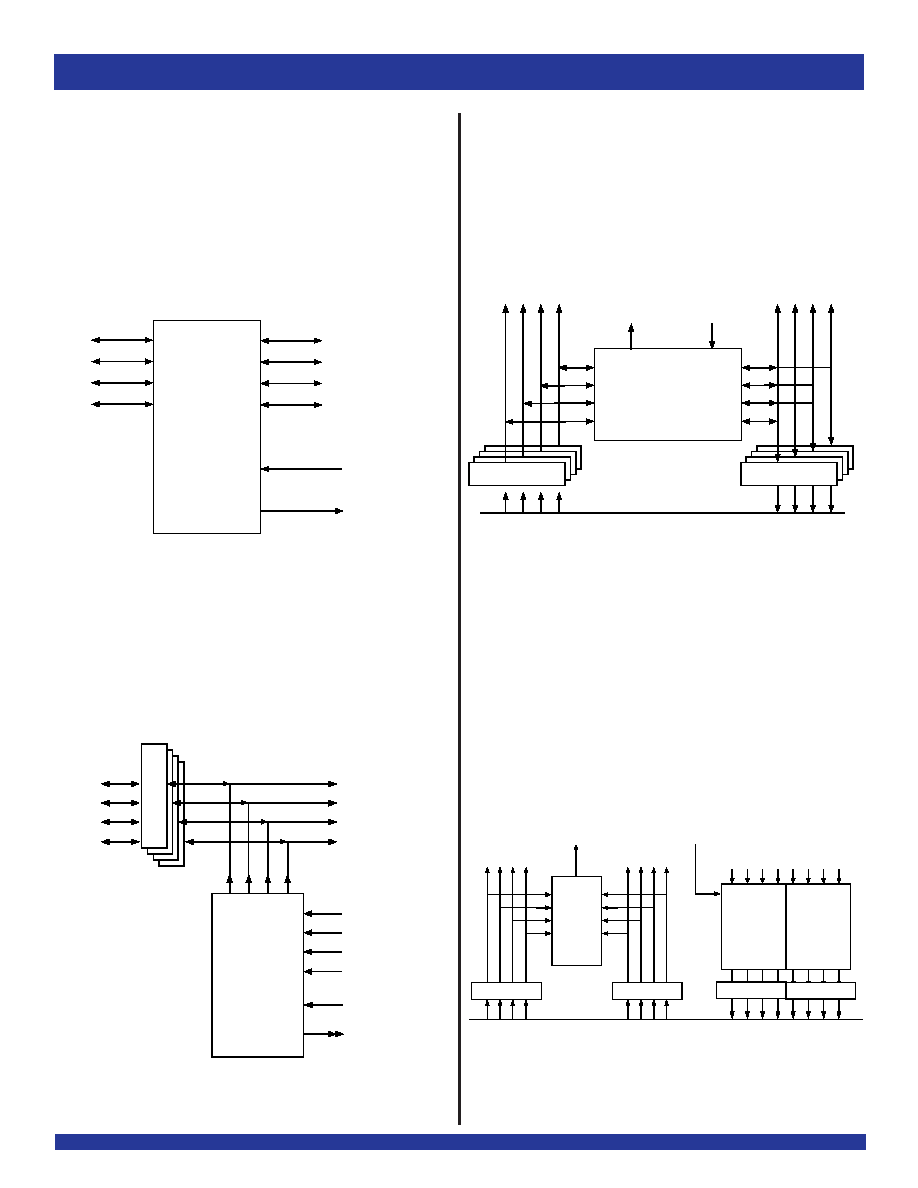

Figure 1. Common I/O Configuration

Figure 3. Bypassed Separate I/O Configuration

SYSTEM CONFIGURATIONS

The IDT49C465 EDC unit can be used in various configurations in an

EDC system. The basic configurations are shown below.

Figure1illustratesabidirectionalconfiguration,whichismostappropriate

for systems using bidirectional memory buses. It is the simplest

configuration to understand and use. During a correction cycle, the

corrected data word can be simultaneously output on both the system

bus and memory bus. During partial-word-write operations, the new

bytes are internally combined with the corrected old bytes for checkbit

generation and writing to memory.

Figure 2 illustrates a separate I/O configuration. This is appropriate

for systems using separate I/O memory buses. This configuration

allows separate input and output memory buses to be used. Corrected

data is output on the SD outputs for the system and for re-write to

memory. Partial word-write bytes are combined externally for writing

and checkbit generation.

Figure 3 illustrates a third configuration which uses external buffers

and is also well-suited for systems using memory with separate I/O

buses. Since data from memory does not need to pass through the part

on every cycle, the EDC system may operate in “bus-watch” mode. As

in the separate I/O configuration, corrected data is output on the SD

outputs.

Figure 4 illustrates the single-chip generate-only mode for the very

fast 64-bit checkbit generation in systems that use separate checkbit-

generate and detect-correct units. If this is not desired, 64-checkbit

generation and correction can be done with just two EDC units. 64-bit

correction is also straightforward, fast, and requires no extra hardware

for the expansion.

EXT.

BU

F

E

R

SD

MD

ED C

CBI

CBO

MEM O R Y

INP UTS

C HE C KBITS

MEMO RY

OUTP UTS

CP U

ED C

CBO

64-BIT

GEN .

ON LY

MEMO RY

IN PUT BU S

CH ECK

BITS OU T

CPU BU S

BUFFER

MEMO RY

IN PUT BU S

BUFFER

BU FFER

CBI

LOW ER

DATA

UPPER

DATA

ED C

EDC

CHEC K

BITS IN

MEMO RY

OUTPUT BUS

Figure 2. Separate I/O Configuration

Figure 4. Separate generate/Correction Units with 64-Bit Checkbit Generation

相关PDF资料 |

PDF描述 |

|---|---|

| IDT49FCT818AEB | 8-BIT, DSP-PIPELINE REGISTER, CDFP24 |

| IDT49FCT818P | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

| IDT49FCT818L | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818LB | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818PB | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT49C465PQFB | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466A | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466APQF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466GB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Error Detection & Correction (EDAC) |

发布紧急采购,3分钟左右您将得到回复。