- 您现在的位置:买卖IC网 > PDF目录67711 > IDT49C465PQF8 (INTEGRATED DEVICE TECHNOLOGY INC) 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 PDF资料下载

参数资料

| 型号: | IDT49C465PQF8 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 算术逻辑单元 |

| 英文描述: | 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 |

| 封装: | PLASTIC, QFP-144 |

| 文件页数: | 38/39页 |

| 文件大小: | 299K |

| 代理商: | IDT49C465PQF8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页

8

COMMERCIAL TEMPERATURE RANGE

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

PIN DESCRIPTIONS (continued)

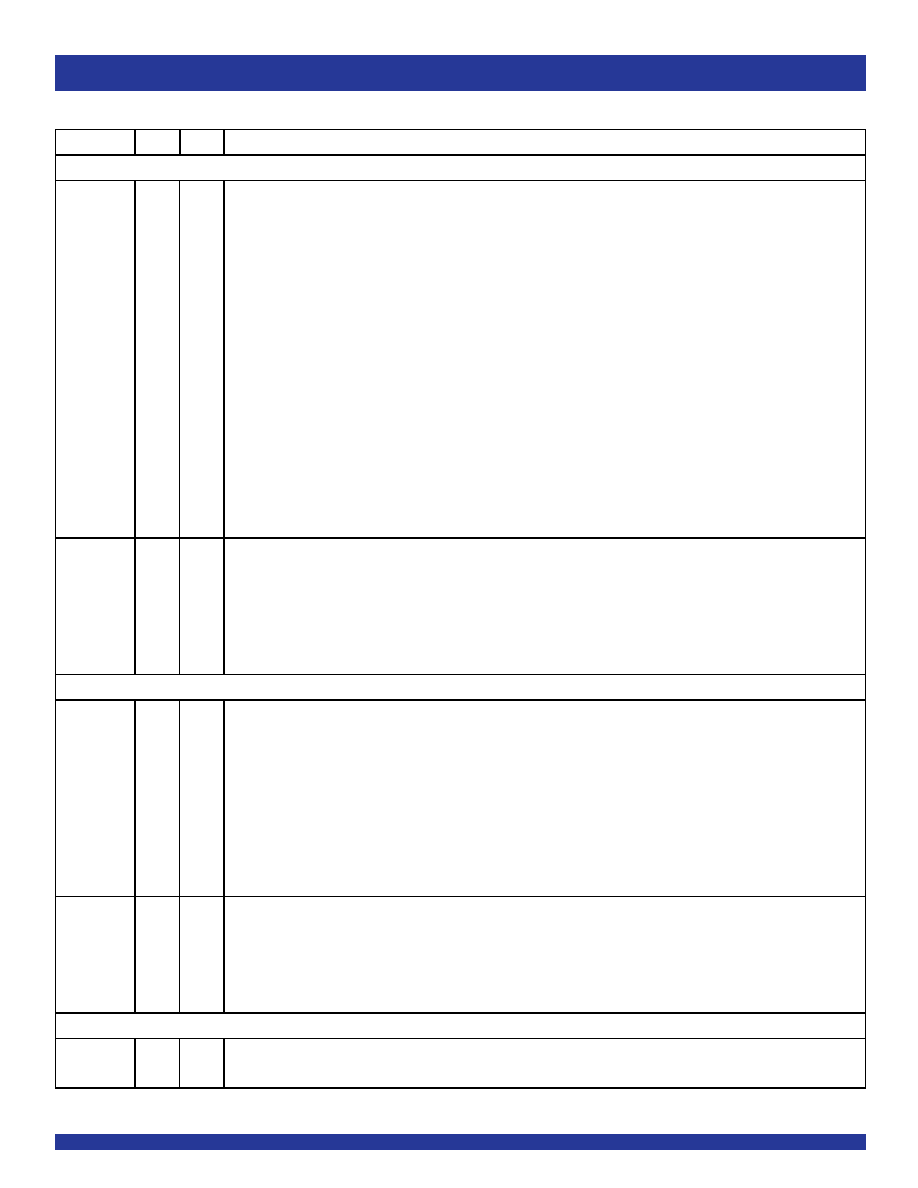

Symbol

I/O

Name and Function

Inputs (continued)

MODE2-0

I

MODE Select: Selects one of the five operating modes.

(x11)

“Normal” Mode: Normal EDC operation (Flow-thru correction and generation).

(x10)

“Generate-Detect” Mode: In this mode, error correction is disabled. Error generation and detection are normal.

(000)

“Error-Data-Output” Mode: Allows the uncorrected data from an error event by the Error-Data register to be read by the

system for diagnostic purposes. The Error-Data Register is cleared by toggling CLEAR LOW. The Syndrome Register and

Error Data Register record the syndrome and uncorrected data from the first error that occurs after they are reset by the CLEAR

pin. The Syndrome Register and Error-Data Register are updated when there is a positive edge on SYNCLK, an error condition

is indicated (ERR = LOW), and the Error Counter indicates zero.

All-Zero-Data Source: In Error-Data-Output Mode, clearing the Error-Data Register provides a source of all-zero-data for

hardware initialization of memory, if this is desired.

(x01)

Diagnostic-output Mode: In this mode, the contents of the Syndrome Register, Error Counter and Error-Type Register are

output on the SD bus. This allows the syndrome bytes for an indicated error to be read by the system for error-logging

purposes. The Syndrome Register and the Error-Data Register are updated when there is a positive edge an SYNCLK, and

error condition is indicated, and the Error Counter indicates zero errors. Thus, the Syndrome Register saves the syndrome that

was present when the first error occurred after the Error Counter was cleared. The Syndrome Register and the Error Counter

are cleared by toggling CLEAR LOW. The Error Counter lets the system tell if more than one error has occurred since the last

time the Syndrome Register or Error Data Register was read.

(100)

Checkbit-Injection Mode: In “Checkbit-Injection” Mode, diagnostic checkbits may be input on the System Data Bus bits 0-7

(see Diagnostic Features - Detailed Description).

CLEAR

I

CLEAR: When the CLEAR pin is taken LOW, the Error-Data Register, the Syndrome Register, the Error Counter, and the Error-

Type Register are cleared.

SYNCLK

I

SYNdrome CLocK: If ERR is LOW, and the Error Counter indicates zero errors, syndrome bits are clocked into the Syndrome

Register and data from the outputs of the Memory Data input latch are clocked into the Error-Data Register on the LOW-to-

HIGH edge of SYNCLK. If ERR is LOW, the Error Counter will increment on the LOW-to-HIGH edge of SYNCLK, unless the

Error Counter indicated fifteen errors.

SCLKEN

I

SynCLK ENable: The SCLKEN enables the SYNCLK signal. SYNCLK is ignored if SCLKEN is HIGH.

Outputs and Enables

CBO0-7

O

CheckBits-Out (00, 01)

Partial CheckBits-Out (10):

CheckBits-Out (11):

In a single EDC system, the checkbits are output to the checkbit memory on the outputs. In the lower slice in a cascaded EDC

system, the “Partial-checkbits” used by the upper slice are generated by the lower slice CBO0-7 bits (Generate path only). In the

upper slice of a cascade, the “Final-Checkbits” appear at these outputs (Generate path only).

CBOE

I

CheckBits Out Enable: Enables CheckBit Output driver when LOW.

SYO0-7

O

SYndrome-Out (00)

Partial SYndrome-Out(10):

Partial CheckBits-Out (11):

In a 32-bit EDC system, the syndrome bits are output on these pins. In the lower slice in a 64-bit cascaded system, the “Partial-

Syndrome” bits appear at these outputs (Detect/Correct path). In the upper slice in a cascaded EDC system, the “Partial-

Checkbits” appear at these outputs (Correct path only). In a 64-bit cascaded system, the “Final-Syndrome” may be accessed in

the “Diagnostic-Output” Mode from either the lower or the upper slice since the final syndrome is contained in both.

ERR

O

ERROR: When in “Normal” and “Detect only” modes, a LOW on this pin indicates that one or more errors have been detected.

ERR is not gated or latched internally.

MERR

O

Multiple ERRor: When in “Normal” and “Detect only” modes, a LOW on this pin indicates that one or more errors have been

detected. MERR is not gated or latched internally.

PERR

O

Parity ERRor: A LOW on this pin indicates a parity error which has resulted from the active bytes defined by the 4 Byte Enable

pins. Parity ERRor (PERR) is not gated or latched internally (see Byte Enable definition).

Power Supply Pins

Vcc 1-10

P+5 Volts

GND 1-12

P

Ground

相关PDF资料 |

PDF描述 |

|---|---|

| IDT49FCT818AEB | 8-BIT, DSP-PIPELINE REGISTER, CDFP24 |

| IDT49FCT818P | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

| IDT49FCT818L | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818LB | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818PB | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT49C465PQFB | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466 | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466A | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466APQF | 制造商:IDT 制造商全称:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466GB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Error Detection & Correction (EDAC) |

发布紧急采购,3分钟左右您将得到回复。