- 您现在的位置:买卖IC网 > PDF目录9894 > IDT72V36110L6BBG (IDT, Integrated Device Technology Inc)IC FIFO SYNC 131KX36 6NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72V36110L6BBG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 23/48页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 131KX36 6NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7M(131K x 36) |

| 数据速率: | 166MHz |

| 访问时间: | 4ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72V36110L6BBG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

3

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

OCTOBER 22, 2008

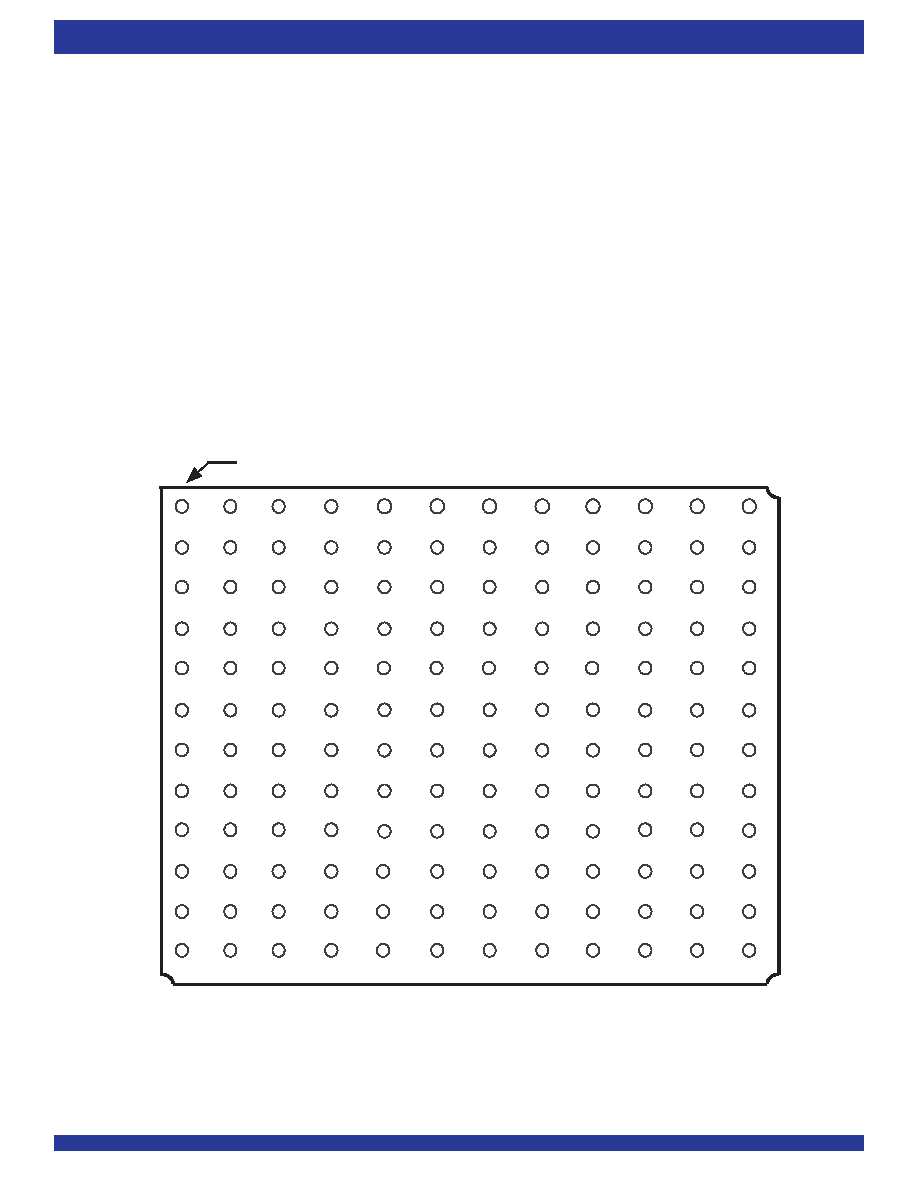

PIN CONFIGURATIONS (CONTINUED)

PBGA: 1mm pitch, 13mm x 13mm (BB144-1, order code: BB)

TOP VIEW

ASYW

WEN

WCLK

PAF

FF/IR

HF

BM

EF

RCLK

REN

OE

Q35

SEN

IW

PRS

LD

MRS

FS0

FS1

ASYR

IP

PFM

RT

Q34

D35

D34

D33

FWFT/SI

OW

VCC

BE

PAE

RM

Q32

Q3

3

D32

D31

D30

VCC

GND

VCC

Q29

Q30

Q31

D29

D26

D27

VCC

Q26

Q27

Q28

D28

D25

D24

Q23

Q24

Q25

D21

D22

D23

Q22

Q21

Q20

D18

D19

D20

VCC

Q19

Q18

Q17

D15

D16

D17

VCC

Q16

Q15

Q14

D12

D13

D14

D3

D0

VCC

TDO

Q2

Q13

Q12

Q11

D10

D6

D4

D1

TMS

TCK

Q0

Q3

Q5

Q10

Q9

D8

D7

D5

D2

TRST

TDI

Q1

Q4

Q6

Q7

Q8

A1 BALL PAD CORNER

A

B

C

D

E

F

G

H

J

K

L

M

12

3

4

5

6

7

8

9

10

11

12

6117 drw02b

GND

VCC

GND

VCC

GND

VCC

GND

D11

D9

VCC

WCLK when

WEN is asserted. During Asynchronous operation only the WR

input is used to write data into the FIFO. Data is written on a rising edge of WR,

the

WEN input should be tied to its active state, (LOW).

TheoutputportcanbeselectedaseitheraSynchronous(clocked)interface,

or Asynchronous interface. During Synchronous operation the output port is

controlled by a Read Clock (RCLK) input and Read Enable (

REN)input. Data

is read from the FIFO on every rising edge of RCLK when

REN is asserted.

During Asynchronous operation only the RD input is used to read data from the

FIFO. Data is read on a rising edge of RD, the

REN input should be tied to its

activestate,LOW.WhenAsynchronousoperationisselectedontheoutputport

the FIFO must be configured for Standard IDT mode, and the

OE input used

to provide three-state control of the outputs, Qn.

The frequencies of both the RCLK and the WCLK signals may vary from 0

tofMAXwithcompleteindependence. Therearenorestrictionsonthefrequency

of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices: IDT

Standard mode and First Word Fall Through (FWFT) mode.

InIDTStandardmode,thefirstwordwrittentoanemptyFIFOwillnotappear

on the data output lines unless a specific read operation is performed. A read

DESCRIPTION (CONTINUED)

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1229BCEP+ | IC ADC 12-BIT 300KSPS 20-QSOP |

| MS27472T24B61SB | CONN RCPT 61POS WALL MT W/SCKT |

| MAX1249AEEE+ | IC ADC 10BIT SERIAL 16-QSOP |

| MAX1174BCUP+ | IC ADC 14BIT 135KSPS 20-TSSOP |

| MAX1065BCUI+ | IC ADC 14BIT 165KSPS 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V36110L6BBG8 | 功能描述:IC FIFO SYNC 131KX36 6NS 144BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF8 | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PFG | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V36110L7-5BB | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。