- 您现在的位置:买卖IC网 > PDF目录9894 > IDT72V36110L6BBG (IDT, Integrated Device Technology Inc)IC FIFO SYNC 131KX36 6NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72V36110L6BBG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 41/48页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 131KX36 6NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7M(131K x 36) |

| 数据速率: | 166MHz |

| 访问时间: | 4ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72V36110L6BBG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页

46

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

OCTOBER 22, 2008

THE INSTRUCTION REGISTER

TheInstructionregisterallowsaninstructiontobeshiftedinseriallyintothe

processor at the rising edge of TCLK.

The Instruction is used to select the test to be performed, or the test data

registertobeaccessed,orboth. Theinstructionshiftedintotheregisterislatched

at the completion of the shifting process when the TAP controller is at Update-

IRstate.

The instruction register must contain 4 bit instruction register-based cells

whichcanholdinstructiondata. Thesemandatorycellsarelocatednearestthe

serial outputs they are the least significant bits.

TEST DATA REGISTER

The Test Data register contains three test data registers: the Bypass, the

Boundary Scan register and Device ID register.

These registers are connected in parallel between a common serial input

and a common serial data output.

The following sections provide a brief description of each element. For a

completedescription,refertotheIEEEStandardTestAccessPortSpecification

(IEEE Std. 1149.1-1990).

TEST BYPASS REGISTER

The register is used to allow test data to flow through the device from TDI

toTDO. Itcontainsasinglestageshiftregisterforaminimumlengthinserialpath.

When the bypass register is selected by an instruction, the shift register stage

is set to a logic zero on the rising edge of TCLK when the TAP controller is in

the Capture-DR state.

The operation of the bypass register should not have any effect on the

operation of the device in response to the BYPASS instruction.

THE BOUNDARY-SCAN REGISTER

The Boundary Scan Register allows serial data TDI be loaded in to or read

out of the processor input/output ports. The Boundary Scan Register is a part

of the IEEE 1149.1-1990 Standard JTAG Implementation.

THE DEVICE IDENTIFICATION REGISTER

The Device Identification Register is a Read Only 32-bit register used to

specify the manufacturer, part number and version of the processor to be

determined through the TAP in response to the IDCODE instruction.

IDT JEDEC ID number is 0xB3. This translates to 0x33 when the parity

is dropped in the 11-bit Manufacturer ID field.

For the IDT72V36100/72V36110, the Part Number field contains the

following values:

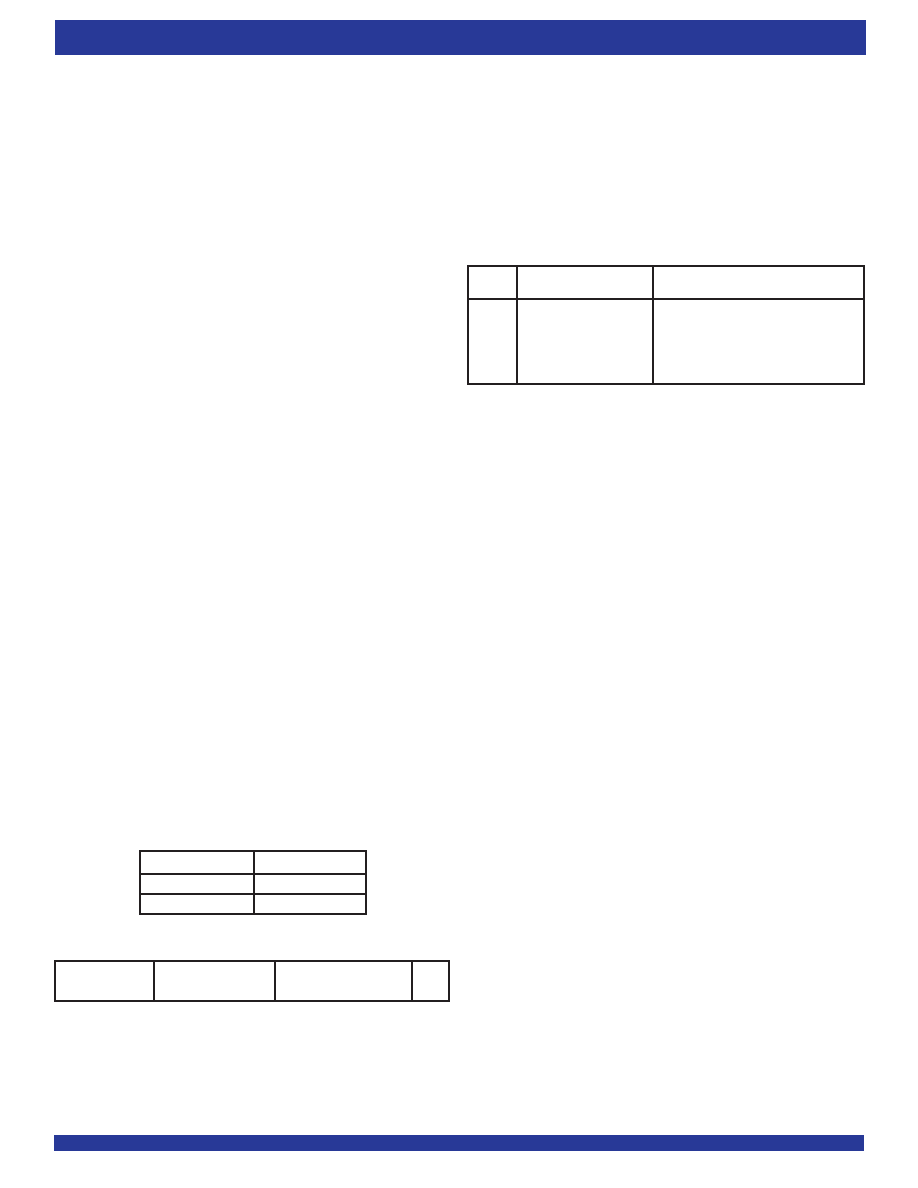

JTAG INSTRUCTION REGISTER

TheInstructionregisterallowsinstructiontobeseriallyinputintothedevice

when the TAP controller is in the Shift-IR state. The instruction is decoded to

perform the following:

Select test data registers that may operate while the instruction is

current. The other test data registers should not interfere with chip

operation and the selected data register.

Definetheserialtestdataregisterpaththatisusedtoshiftdatabetween

TDI and TDO during data register scanning.

The Instruction Register is a 4 bit field (i.e.IR3, IR2, IR1, IR0) to decode 16

different possible instructions. Instructions are decoded as follows.

Hex

Instruction

Function

Value

0x00

EXTEST

Select Boundary Scan Register

0x02

IDCODE

Select Chip Identification data register

0x01

SAMPLE/PRELOAD

Select Boundary Scan Register

0x03

HIGH-IMPEDANCE

JTAG

0x0F

BYPASS

Select Bypass Register

Table 6. JTAG Instruction Register Decoding

The following sections provide a brief description of each instruction. For

acompletedescriptionrefertotheIEEEStandardTestAccessPortSpecification

(IEEE Std. 1149.1-1990).

EXTEST

The required EXTEST instruction places the IC into an external boundary-

testmodeandselectstheboundary-scanregistertobeconnectedbetweenTDI

and TDO. During this instruction, the boundary-scan register is accessed to

drive test data off-chip via the boundary outputs and receive test data off-chip

via the boundary inputs. As such, the EXTEST instruction is the workhorse of

IEEE. Std 1149.1, providing for probe-less testing of solder-joint opens/shorts

and of logic cluster function.

IDCODE

TheoptionalIDCODEinstructionallowstheICtoremaininitsfunctionalmode

andselectstheoptionaldeviceidentificationregistertobeconnectedbetween

TDIandTDO.Thedeviceidentificationregisterisa32-bitshiftregistercontaining

information regarding the IC manufacturer, device type, and version code.

Accessingthedeviceidentificationregisterdoesnotinterferewiththeoperation

oftheIC.Also,accesstothedeviceidentificationregistershouldbeimmediately

available, via a TAP data-scan operation, after power-up of the IC or after the

TAP has been reset using the optional

TRSTpinorbyotherwisemovingtothe

Test-Logic-Resetstate.

SAMPLE/PRELOAD

The required SAMPLE/PRELOAD instruction allows the IC to remain in a

normalfunctionalmodeandselectstheboundary-scanregistertobeconnected

between TDI and TDO. During this instruction, the boundary-scan register can

be accessed via a date scan operation, to take a sample of the functional data

enteringandleavingtheIC.Thisinstructionisalsousedtopreloadtestdatainto

the boundary-scan register before loading an EXTEST instruction.

Device

Part# Field

IDT72V36100

04DE

IDT72V36110

04DF

IDT72V36100/72V36110 JTAG Device Identification Register

31(MSB)

28 27

12 11

1 0(LSB)

Version (4 bits)

Part Number (16-bit) Manufacturer ID (11-bit)

0X0

0X33

1

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1229BCEP+ | IC ADC 12-BIT 300KSPS 20-QSOP |

| MS27472T24B61SB | CONN RCPT 61POS WALL MT W/SCKT |

| MAX1249AEEE+ | IC ADC 10BIT SERIAL 16-QSOP |

| MAX1174BCUP+ | IC ADC 14BIT 135KSPS 20-TSSOP |

| MAX1065BCUI+ | IC ADC 14BIT 165KSPS 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V36110L6BBG8 | 功能描述:IC FIFO SYNC 131KX36 6NS 144BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF8 | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PFG | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V36110L7-5BB | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。