- 您现在的位置:买卖IC网 > PDF目录9894 > IDT72V36110L6BBG (IDT, Integrated Device Technology Inc)IC FIFO SYNC 131KX36 6NS 144BGA PDF资料下载

参数资料

| 型号: | IDT72V36110L6BBG |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 5/48页 |

| 文件大小: | 0K |

| 描述: | IC FIFO SYNC 131KX36 6NS 144BGA |

| 标准包装: | 1 |

| 系列: | 72V |

| 功能: | 同步 |

| 存储容量: | 4.7M(131K x 36) |

| 数据速率: | 166MHz |

| 访问时间: | 4ns |

| 电源电压: | 3.15 V ~ 3.45 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-BGA |

| 供应商设备封装: | 144-PBGA(13x13) |

| 包装: | 托盘 |

| 其它名称: | 72V36110L6BBG |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

13

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V36100/72V36110 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

65,536 x 36 and 131,072 x 36

OCTOBER 22, 2008

the

LD (Load) pin. During Master Reset, the state of the LD input determines

whether serial or parallel flag offset programming is enabled. A HIGH on

LD

duringMasterResetselectsserialloadingofoffsetvalues. ALOWon

LDduring

Master Reset selects parallel loading of offset values.

In addition to loading offset values into the FIFO, it is also possible to read

the current offset values. Offset values can be read via the parallel output port

Q0-Qn, regardless of the programming mode selected (serial or parallel). It is

not possible to read the offset values in serial fashion.

Figure 3, Programmable Flag Offset Programming Sequence, summaries

thecontrolpinsandsequenceforbothserialandparallelprogrammingmodes.

For a more detailed description, see discussion that follows.

Theoffsetregistersmaybeprogrammed(andreprogrammed)anytimeafter

Master Reset, regardless of whether serial or parallel programming has been

selected. Valid programming ranges are from 0 to D-1.

SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIM-

ING SELECTION

The IDT72V36100/72V36110 can be configured during the Master Reset

cycle with either synchronous or asynchronous timing for

PAFandPAEflags

by use of the PFM pin.

If synchronous

PAF/PAE configuration is selected (PFM, HIGH during

MRS), the PAF is asserted and updated on the rising edge of WCLK only and

not RCLK. Similarly,

PAEisassertedandupdatedontherisingedgeofRCLK

only and not WCLK. For detail timing diagrams, see Figure 17 for synchronous

PAF timing and Figure 18 for synchronous PAE timing.

If asynchronous

PAF/PAE configuration is selected (PFM, LOW during

MRS),thePAFisassertedLOWontheLOW-to-HIGHtransitionofWCLKand

PAFisresettoHIGHontheLOW-to-HIGHtransitionofRCLK. Similarly,PAE

isassertedLOWontheLOW-to-HIGHtransitionofRCLK.

PAEisresettoHIGH

ontheLOW-to-HIGHtransitionofWCLK.Fordetailtimingdiagrams,seeFigure

19 for asynchronous

PAFtimingandFigure20forasynchronousPAEtiming.

IDT72V36100, 72V36110

LD

FSEL1

FSEL0

Offsets n,m

L

H

L

16,383

L

H

8,191

L

H

4,095

H

L

2,047

H

L

1,023

HL

H

511

HHH

255

LLL

127

LD

FSEL1

FSEL0

Program Mode

H

X

Serial(3)

L

X

Parallel(4)

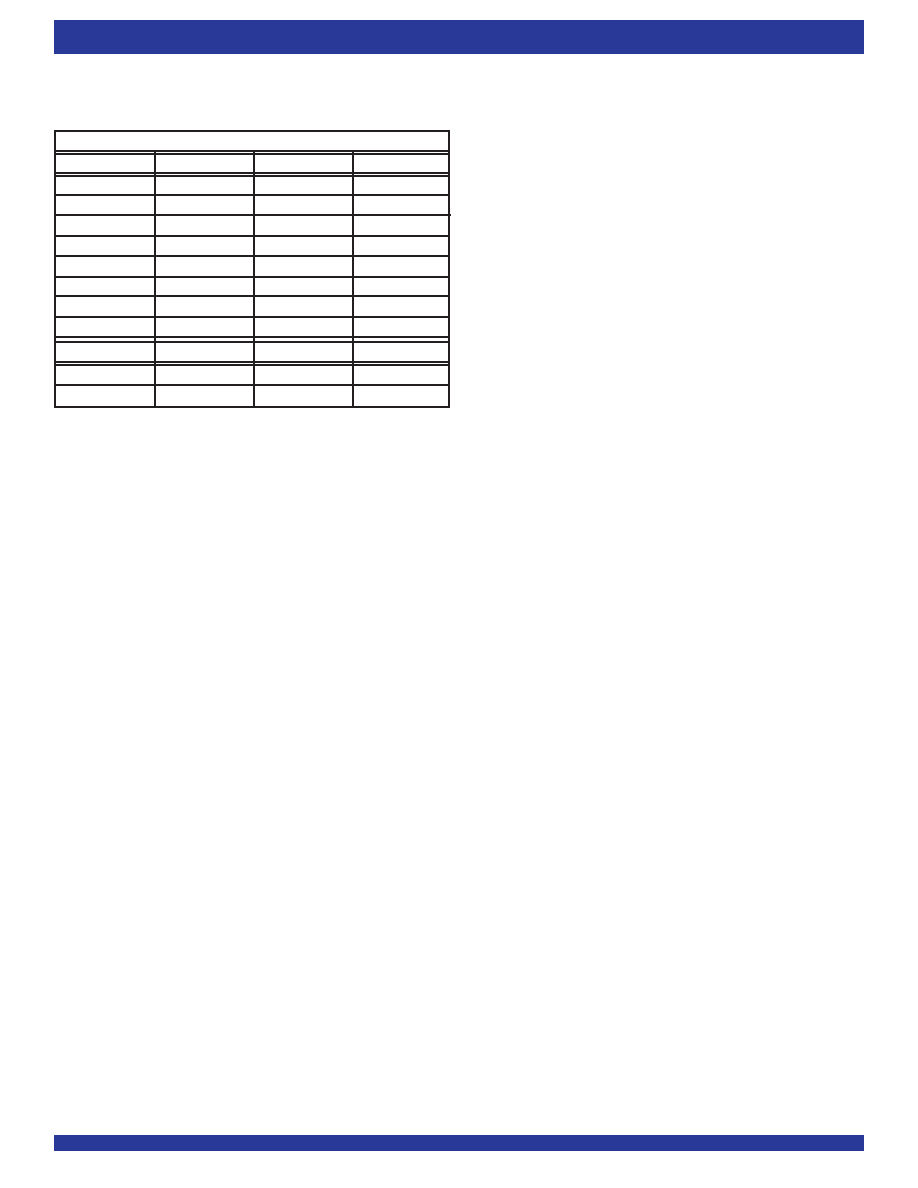

TABLE 2 — DEFAULT PROGRAMMABLE

FLAG OFFSETS

NOTES:

1. n = empty offset for

PAE.

2. m = full offset for

PAF.

3. As well as selecting serial programming mode, one of the default values will also

be loaded depending on the state of FSEL0 & FSEL1.

4. As well as selecting parallel programming mode, one of the default values will

also be loaded depending on the state of FSEL0 & FSEL1.

PROGRAMMING FLAG OFFSETS

FullandEmptyFlagoffsetvaluesareuserprogrammable.TheIDT72V36100/

72V36110haveinternalregistersfortheseoffsets.Thereareeightdefaultoffset

valuesselectableduringMasterReset. TheseoffsetvaluesareshowninTable

2.OffsetvaluescanalsobeprogrammedintotheFIFOinoneoftwoways;serial

or parallel loading method. The selection of the loading method is done using

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1229BCEP+ | IC ADC 12-BIT 300KSPS 20-QSOP |

| MS27472T24B61SB | CONN RCPT 61POS WALL MT W/SCKT |

| MAX1249AEEE+ | IC ADC 10BIT SERIAL 16-QSOP |

| MAX1174BCUP+ | IC ADC 14BIT 135KSPS 20-TSSOP |

| MAX1065BCUI+ | IC ADC 14BIT 165KSPS 28TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V36110L6BBG8 | 功能描述:IC FIFO SYNC 131KX36 6NS 144BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PF8 | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

| IDT72V36110L6PFG | 功能描述:IC FIFO SYNC 131KX36 6NS 128QFP RoHS:是 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:90 系列:74ABT 功能:同步,双端口 存储容量:4.6K(64 x 36 x2) 数据速率:67MHz 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:120-LQFP 裸露焊盘 供应商设备封装:120-HLQFP(14x14) 包装:托盘 产品目录页面:1005 (CN2011-ZH PDF) 其它名称:296-3984 |

| IDT72V36110L7-5BB | 功能描述:IC FIFO 131KX36 7-5NS 144BGA RoHS:否 类别:集成电路 (IC) >> 逻辑 - FIFO 系列:72V 标准包装:15 系列:74F 功能:异步 存储容量:256(64 x 4) 数据速率:- 访问时间:- 电源电压:4.5 V ~ 5.5 V 工作温度:0°C ~ 70°C 安装类型:通孔 封装/外壳:24-DIP(0.300",7.62mm) 供应商设备封装:24-PDIP 包装:管件 其它名称:74F433 |

发布紧急采购,3分钟左右您将得到回复。