- 您现在的位置:买卖IC网 > PDF目录4588 > IDT72V51246L6BB8 (IDT, Integrated Device Technology Inc)IC FLOW CTRL MULTI QUEUE 256-BGA PDF资料下载

参数资料

| 型号: | IDT72V51246L6BB8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 18/56页 |

| 文件大小: | 0K |

| 描述: | IC FLOW CTRL MULTI QUEUE 256-BGA |

| 标准包装: | 1,000 |

| 类型: | 多队列流量控制 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BBGA |

| 供应商设备封装: | 256-BGA(17x17) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V51246L6BB8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

25

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72V51236/72V51246/72V51256 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES

(4 QUEUES) 36 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

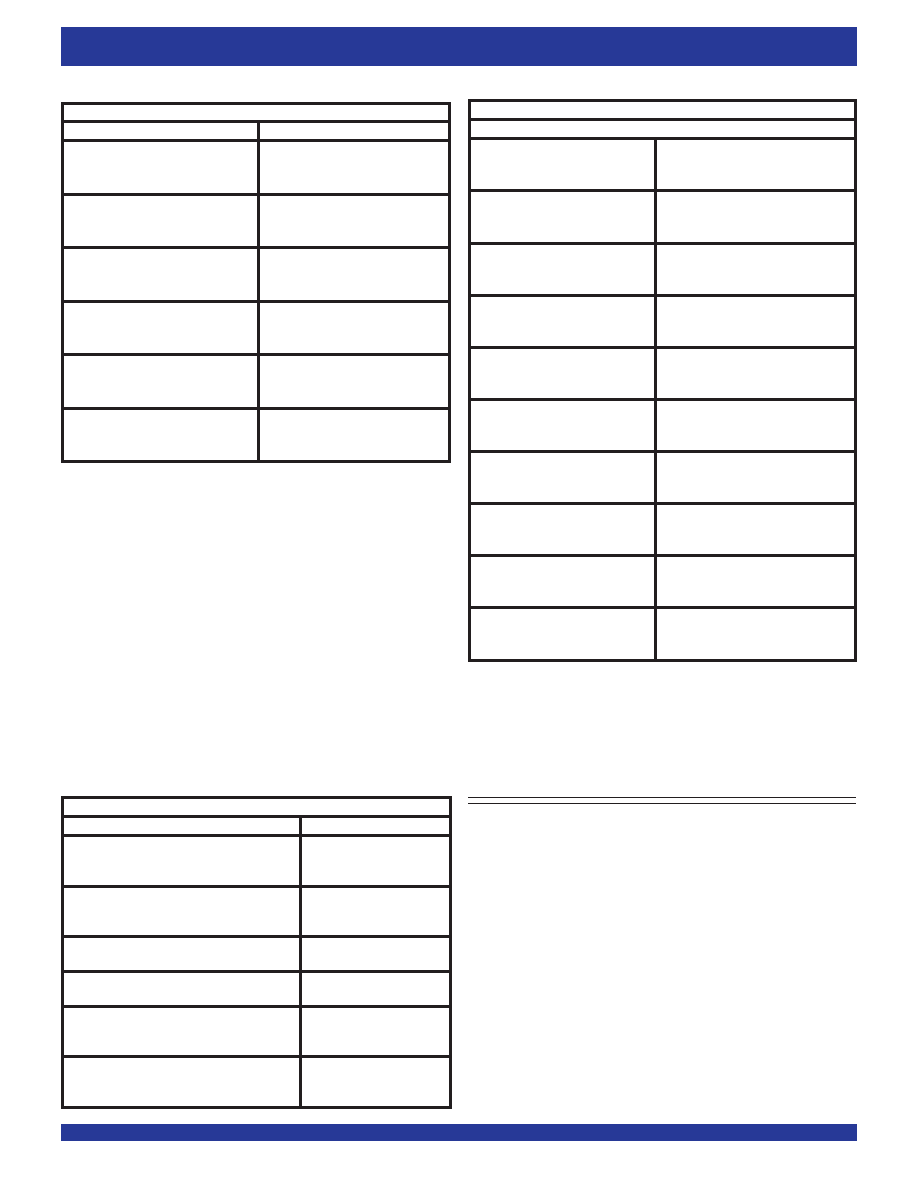

TABLE 4 — FLAG OPERATION BOUNDARIES & TIMING

Output Valid,

OV Flag Boundary

I/O Set-Up

OV Boundary Condition

In36 to out36 (Almost Empty Mode)

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 1 below for timing)

when the 1st Word is written in)

In36 to out36 (Packet Mode)

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 2 below for timing)

when the 1st Word is written in)

In36 to out18

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 1 below for timing)

when the 1st Word is written in)

In36 to out9

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 1 below for timing)

when the 1st Word is written in)

In18 to out36

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 1 below for timing)

when the 1st Word is written in)

In9 to out36

OV Goes LOW after 1st Write

(Both ports selected for same queue

(see note 1 below for timing)

when the 1st Word is written in)

NOTE:

1.

OV Timing

Assertion:

Write to

OV LOW: tSKEW1 + RCLK + tROV

If tSKEW1 is violated there may be 1 added clock: tSKEW1 + 2 RCLK + tROV

De-assertion:

Read Operation to

OV HIGH: tROV

2.

OV Timing when in Packet Mode (36 in to 36 out only)

Assertion:

Write to

OV LOW: tSKEW4 + RCLK + tROV

If tSKEW4 is violated there may be 1 added clock: tSKEW4 + 2 RCLK + tROV

De-assertion:

Read Operation to

OV HIGH: tROV

Programmable Almost Full Flag,

PAF & PAFn Bus Boundary

I/O Set-Up

PAF & PAFn Boundary

in36 to out36

PAF/PAFn Goes LOW after

(Both ports selected for same queue when the 1st

D+1-m Writes

Word is written in until the boundary is reached)

(see note below for timing)

in36 to out36

PAF/PAFn Goes LOW after

(Write port only selected for same queue when the D-m Writes

1st Word is written in until the boundary is reached) (see note below for timing)

in36 to out18

PAF/PAFn Goes LOW after

D-mWrites(seebelowfortiming)

in36 to out9

PAF/PAFn Goes LOW after

D-mWrites(seebelowfortiming)

in18 to out36

PAF/PAFn Goes LOW after

([D+1-m] x 2) Writes

(see note below for timing)

in9 to out36

PAF/PAFn Goes LOW after

([D+1-m] x 4) Writes

(seenotebelowfortiming)

NOTE:

D = Queue Depth

m = Almost Full Offset value.

Default values:

if DF is LOW at Master Reset then m = 8

if DF is HIGH at Master Reset then m= 128

PAF Timing

Assertion:

Write Operation to

PAF LOW: 2 WCLK + tWAF

De-assertion: Read to

PAF HIGH: tSKEW2 + WCLK + tWAF

If tSKEW2 is violated there may be 1 added clock: tSKEW2 + 2 WCLK + tWAF

PAFn Timing

Assertion:

Write Operation to

PAFn LOW: 2 WCLK* + tPAF

De-assertion: Read to

PAFn HIGH: tSKEW3 + WCLK* + tPAF

If tSKEW3 is violated there may be 1 added clock: tSKEW3 + 2 WCLK* + tPAF

* If a queue switch is occurring on the write port at the point of flag assertion or de-assertion

there may be one additional WCLK clock cycle delay.

NOTE:

D = Queue Depth

FF Timing

Assertion:

Write Operation to

FF LOW: tWFF

De-assertion:

Read to

FF HIGH: tSKEW1 + tWFF

If tSKEW1 is violated there may be 1 added clock: tSKEW1+WCLK +tWFF

Full Flag,

FF Boundary

I/O Set-Up

FF Boundary Condition

In36 to out36

FF Goes LOW after D+1 Writes

(Both ports selected for same queue

(see note below for timing)

when the 1st Word is written in)

In36 to out36

FF Goes LOW after D Writes

(Write port only selected for queue

(see note below for timing)

when the 1st Word is written in)

In36 to out18

FF Goes LOW after D Writes

(Both ports selected for same queue

(see note below for timing)

when the 1st Word is written in)

In36 to out18

FF Goes LOW after D Writes

(Write port only selected for queue

(see note below for timing)

when the 1st Word is written in)

In36 to out9

FF Goes LOW after D Writes

(Both ports selected for same queue

(see note below for timing)

when the 1st Word is written in)

In36 to out9

FF Goes LOW after D Writes

(Write port only selected for queue

(see note below for timing)

when the 1st Word is written in)

In18 to out36

FF Goes LOW after ([D+1] x 2) Writes

(Both ports selected for same queue

(see note below for timing)

when the 1st Word is written in)

In18 to out36

FF Goes LOW after (D x 2) Writes

(Write port only selected for queue

(see note below for timing)

when the 1st Word is written in)

In9 to out36

FF Goes LOW after ([D+1] x 4) Writes

(Both ports selected for same queue

(see note below for timing)

when the 1st Word is written in)

In9 to out36

FF Goes LOW after (D x 4) Writes

(Write port only selected for queue

(see note below for timing)

when the 1st Word is written in)

相关PDF资料 |

PDF描述 |

|---|---|

| LFXP6E-4Q208I | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6C-5Q208C | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6C-4Q208I | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6E-4QN208I | IC FPGA 5.8KLUTS 208PQFP |

| LFXP6E-5QN208C | IC FPGA 5.8KLUTS 208PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V51246L7-5BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51246L7-5BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51246L7-5BBI | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。