- 您现在的位置:买卖IC网 > PDF目录4588 > IDT72V51246L6BB8 (IDT, Integrated Device Technology Inc)IC FLOW CTRL MULTI QUEUE 256-BGA PDF资料下载

参数资料

| 型号: | IDT72V51246L6BB8 |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 56/56页 |

| 文件大小: | 0K |

| 描述: | IC FLOW CTRL MULTI QUEUE 256-BGA |

| 标准包装: | 1,000 |

| 类型: | 多队列流量控制 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-BBGA |

| 供应商设备封装: | 256-BGA(17x17) |

| 包装: | 带卷 (TR) |

| 其它名称: | 72V51246L6BB8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页

9

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

IDT72V51236/72V51246/72V51256 3.3V, MULTI-QUEUE FLOW-CONTROL DEVICES

(4 QUEUES) 36 BIT WIDE CONFIGURATION 589,824, 1,179,648 and 2,359,296 bits

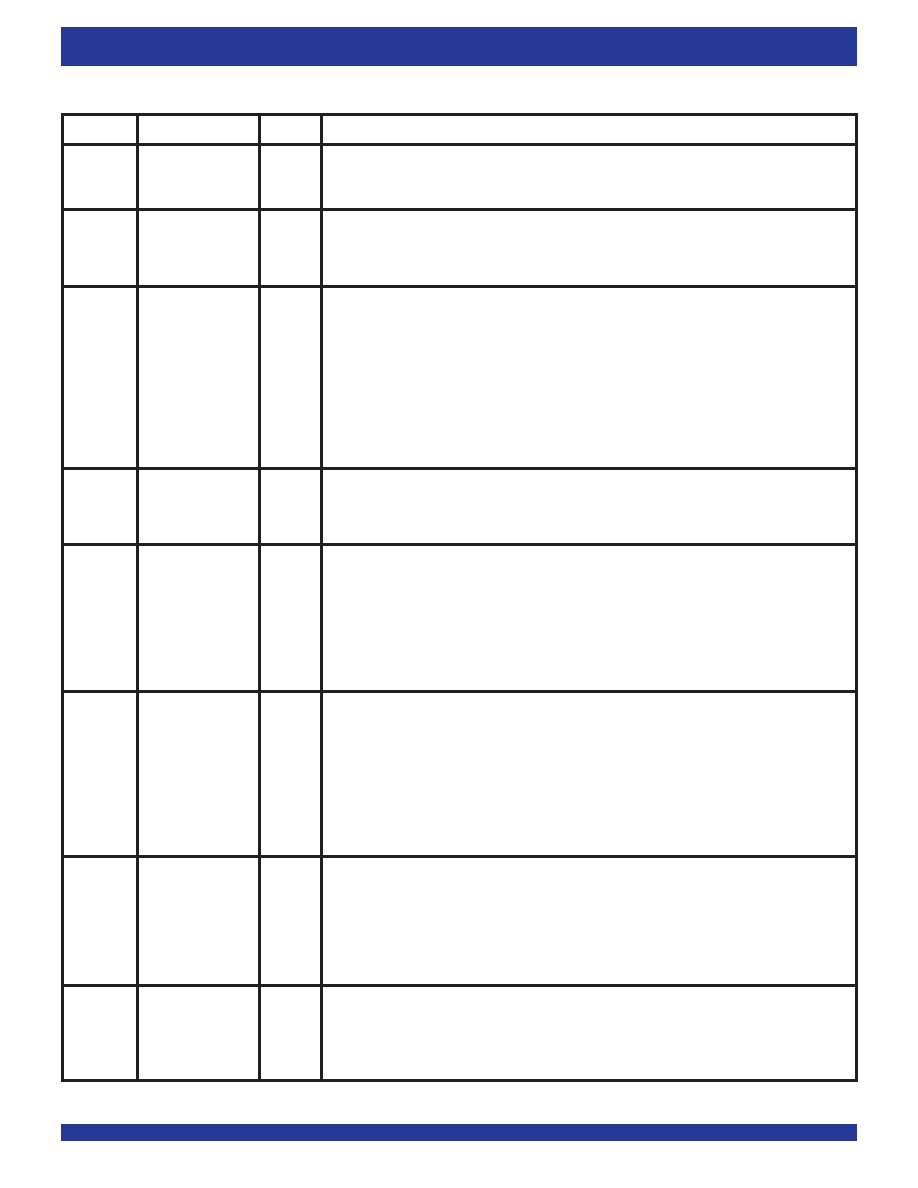

OW(1)

OutputWidth

LVTTL

This pin is setup during Master Reset and must not toggle during any device operation. This pin is used

INPUT

in conjunction with IW and BM to setup the data input and output bus widths to be a combination of x9,

x18 or x36, (providing that one port is x36).

PAE

Programmable

LVTTL

This pin provides the Almost-Empty flag status for the queue that has been selected on the output port

Almost-EmptyFlag

OUTPUT

for read operations, (selected via RCLK, RDADD and RADEN). This pin is LOW when the selected

queue is almost-empty. This flag output may be duplicated on one of the

PAEn bus lines. This flag is

synchronized to RCLK.

PAEn/PRn

Programmable

LVTTL

On the 4Q device the

PAEn/ PRn bus is 4 bits wide. During a Master Reset this bus is setup for either

Almost-EmptyFlag

OUTPUT

Almost Empty mode or Packet mode. This output bus provides

PAE/ PRn status of all 4 queues, within

Bus/Packet Ready

a selected device. During Queue read/write operations these outputs provide programmable empty

Flag Bus

flagstatusorpacketreadystatus,ineitherdirectorpolledmode.Themodeofflagoperationisdetermined

during master reset via the state of the FM input. This flag bus is capable of High-Impedance state, this

is important during expansion of multi-queue devices. During direct operation the

PAEn/ PRn bus is

updated to show the

PAE/PRstatusofqueueswithinaselecteddevice.SelectionismadeusingRCLK,

ESTR and RDADD. During Polled operation the

PAEn/ PRn bus is loaded with the PAE/ PRn status

of multi-queue flow-control devices sequentially based on the rising edge of RCLK.

PAEorPRoperation

is determined by the state of PKT during master reset.

PAF

Programmable

LVTTL

This pin provides the Almost-Full flag status for the queue that has been selected on the input port for

Almost-FullFlag

OUTPUT

write operations, (selected via WCLK, WRADD and WADEN). This pin is LOW when the selected queue

is almost-full. This flag output may be duplicated on one of the

PAFnbuslines.Thisflagissynchronized

toWCLK.

PAFn

Programmable

LVTTL

On the 4Q device the

PAFnbusis4bitswide.ThisoutputbusprovidesPAFstatusofall4queues,within

Almost-Full Flag Bus

OUTPUT

a selected device. During Queue read/write operations these outputs provide programmable full flag

status, in either direct or polled mode. The mode of flag operation is determined during master reset

via the state of the FM input. This flag bus is capable of High-Impedance state, this is important during

expansion of multi-queue devices. During direct operation the

PAFn bus is updated to show the PAF

statusofaqueueswithinaselecteddevice.SelectionismadeusingWCLK,FSTR,WRADDandWADEN.

During Polled operation the

PAFnbusisloadedwiththePAFstatusofmulti-queueflow-controldevices

sequentially based on the rising edge of WCLK.

PKT(1)

Packet Mode

LVTTL

The state of this pin during a Master Reset will determine whether the part is operating in Packet mode

INPUT

providing both a Packet Ready (

PR) output and a Programmable Almost Empty (PAE) discrete output,

or standard mode, providing a (

PAE) output only. If this pin is HIGH during Master Reset the part will

operate in packet mode, if it is LOW then almost empty mode. If packet mode has been selected the read

port flag bus becomes packet ready flag bus,

PRn and the discrete packet ready flag, PR is functional.

If almost empty operation has been selected then the flag bus provides almost empty status,

PAEnand

thediscretealmostemptyflag,

PAEisfunctional,thePRflagisinactiveandshouldnotbeconnected.Packet

Ready utilizes user marked locations to identify start and end of packets being written into the device.

Packet Mode can only be selected if both the input port width and output port width are 36 bits.

PR

Packet Ready Flag

LVTTL

If packet mode has been selected this flag output provides Packet Ready status of the queue selected

for read operations. During a master reset the state of the PKT input determines whether Packet mode

of operation will be used. If Packet mode is selected, then the condition of the

PR flag andOV signalare

asserted indicates a packet is ready for reading. The user must mark the start of a packet and the end

of a packet when writing data into a queue. Using these Start Of Packet (SOP) and End Of Packet

(EOP) markers, the multi-queue device sets

PR LOW if one or more “complete” packets are available

in the queue. A complete packet(s) must be written before the user is allowed to switch queues.

PRS

PartialReset

LVTTL

APartialResetcanbeperformedonasinglequeueselectedwithinthemulti-queuedevice.BeforeaPartial

INPUT

Reset can be performed on a queue, that queue must be selected on both the write port and read port

2 clock cycles before the reset is performed. A Partial Reset is then performed by taking

PRS LOW for

one WCLK cycle and one RCLK cycle. The Partial Reset will only reset the read and write pointers to

the first memory location, none of the devices configuration will be changed.

PIN DESCRIPTIONS (CONTINUED)

Symbol

Name

I/O TYPE

Description

相关PDF资料 |

PDF描述 |

|---|---|

| LFXP6E-4Q208I | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6C-5Q208C | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6C-4Q208I | IC FPGA 5.8KLUTS 142I/O 208-PQFP |

| LFXP6E-4QN208I | IC FPGA 5.8KLUTS 208PQFP |

| LFXP6E-5QN208C | IC FPGA 5.8KLUTS 208PQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IDT72V51246L7-5BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51246L7-5BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51246L7-5BBI | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| IDT72V51253L6BB8 | 功能描述:IC FLOW CTRL MULTI QUEUE 256-BGA RoHS:否 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。