- 您现在的位置:买卖IC网 > PDF目录16076 > IPR-NCO (Altera)IP NCO COMPILER RENEW PDF资料下载

参数资料

| 型号: | IPR-NCO |

| 厂商: | Altera |

| 文件页数: | 19/54页 |

| 文件大小: | 0K |

| 描述: | IP NCO COMPILER RENEW |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | 数控振荡器编译器 |

| 许可证: | 续用许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

�� �

�

�

�Chapter� 2:� Getting� Started�

�2–7�

�MegaWizard� Plug-In� Manager� Flow�

�Table� 2–1� describes� the� generated� files� and� other� files� that� may� be� in� your� project�

�directory.� The� names� and� types� of� files� specified� in� the� report� vary� based� on�

�whether� you� created� your� design� with� VHDL� or� Verilog� HDL.�

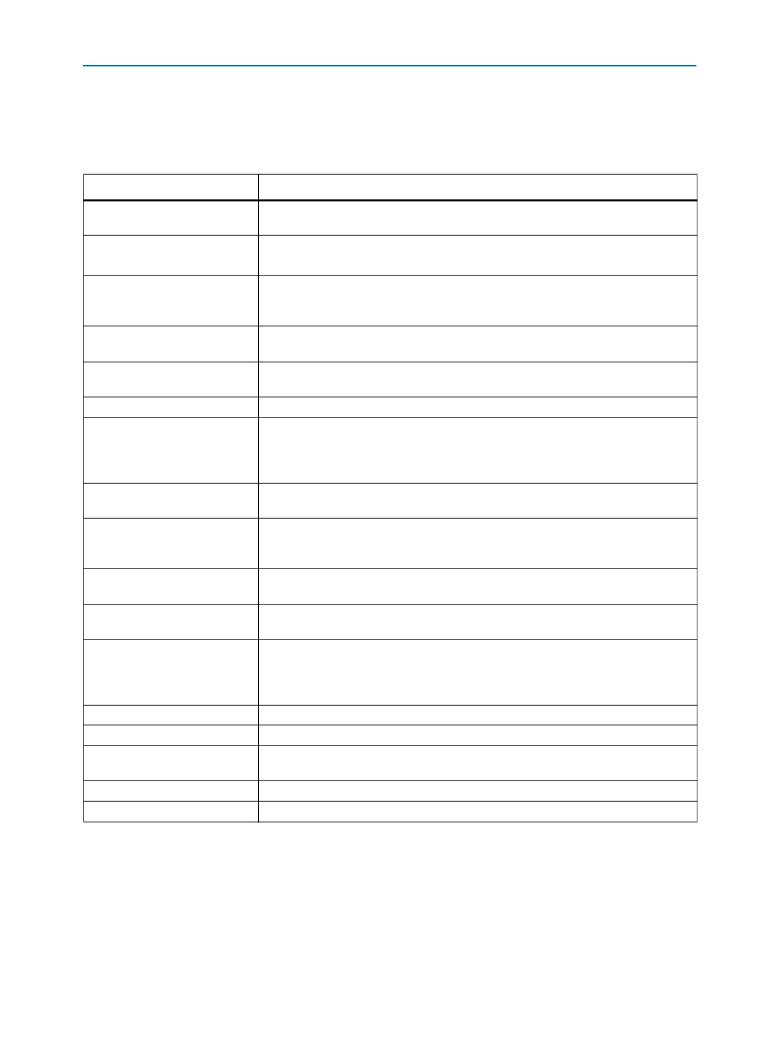

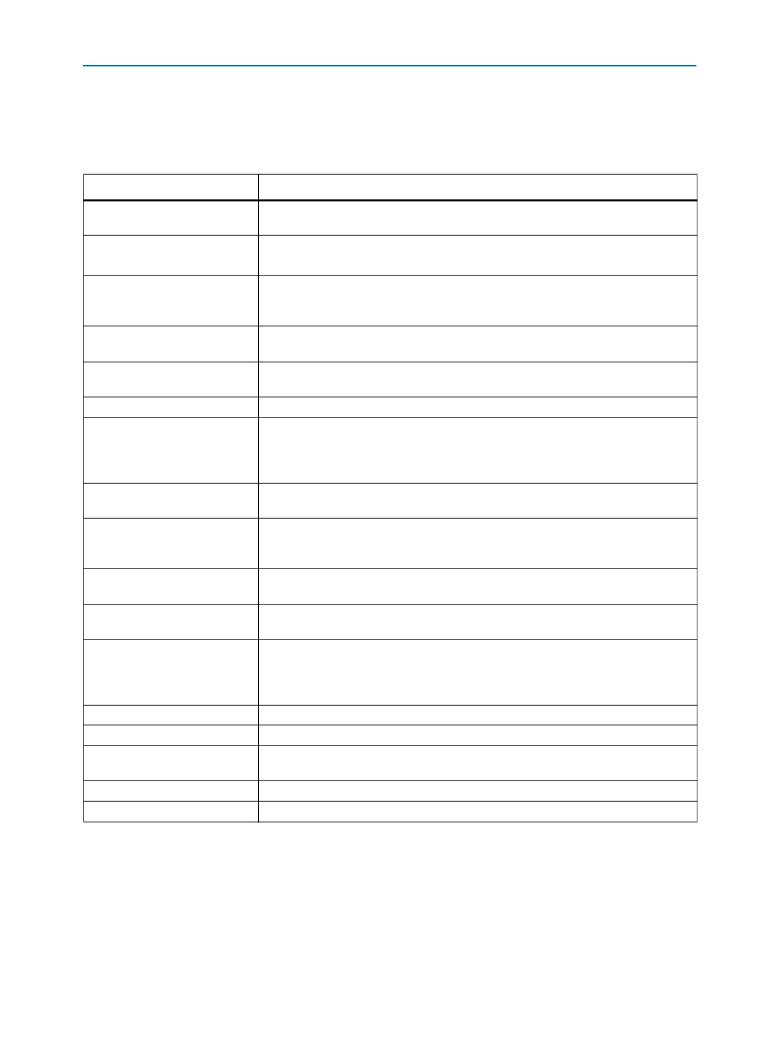

�Table� 2–1.� IP� Toolbench� Files�

�Filename� (1)� ,� (2)�

�<� entity� name� >.v�

�<� variation� name� >_vho_msim.tcl�

�<� variation� name� >_vo_msim.tcl�

�<� variation� name� >_tb.v� or�

�<� variation� name� >_tb.vhd�

�<� variation� name� >� .bsf�

�<� variation� name� >� .cmp�

�<� variation� name� >� .html�

�<� variation� name� >.qip�

�<� variation� name� >.vec�

�<� variation� name� >.vhd� or� .v�

�<� variation� name� >.vho� or�

�<� variation� name� >.vo�

�<� variation� name� >_bb.v�

�<� variation� name� >� _cos_c.hex,�

�<� variation� name� >� _cos_f.hex,�

�<� variation� name� >� _sin_c.hex,�

�<� variation� name� >� _sin_f.hex�

�<� variation� name� >� _syn.v�

�<� variation� name� >� _model.m�

�<� variation� name� >_nativelink.tcl�

�<� variation� name� >� _tb.m�

�<� variation� name� >_wave.do�

�Description�

�Generated� synthesizable� netlist.� This� file� is� required� for� Quartus� II� synthesis.� It� will� be�

�added� to� your� Quartus� II� project.�

�ModelSim� TCL� Script� that� runs� the� VHDL� or� Verilog� HDL� IP� functional� simulation� model�

�and� generated� VHDL� or� Verilog� testbench� in� the� ModelSim� simulation� software.�

�A� VHDL� or� Verilog� HDL� testbench� file� for� the� MegaCore� function� variation.� The� VHDL� file�

�is� generated� when� a� VHDL� top� level� has� been� chosen� or� the� Verilog� HDL� file� when� a�

�Verilog� HDL� top� level� has� been� chosen.�

�Quartus� II� symbol� file� for� the� MegaCore� function� variation.� You� can� use� this� file� in� the�

�Quartus� II� block� diagram� editor.�

�A� VHDL� component� declaration� file� for� the� MegaCore� function� variation.� Add� the�

�contents� of� this� file� to� any� VHDL� architecture� that� instantiates� the� MegaCore� function.�

�A� MegaCore� function� report� file� in� hypertext� markup� language� format.�

�A� single� Quartus� II� IP� file� is� generated� that� contains� all� of� the� assignments� and� other�

�information� required� to� process� your� MegaCore� function� variation� in� the� Quartus� II�

�compiler.� You� are� prompted� to� add� this� file� to� the� current� Quartus� II� project� when� you�

�exit� from� the� MegaWizard.�

�Quartus� II� vector� File.� This� file� provides� simulation� test� vectors� to� be� used� for� simulating�

�the� customized� NCO� MegaCore� function� variation� with� the� Quartus� II� software.�

�A� VHDL� or� Verilog� HDL� file� that� defines� a� VHDL� or� Verilog� HDL� top-level� description� of�

�the� custom� MegaCore� function� variation.� Instantiate� the� entity� defined� by� this� file� inside�

�of� your� design.� Include� this� file� when� compiling� your� design� in� the� Quartus� II� software.�

�A� VHDL� or� Verilog� HDL� output� file� that� defines� the� IP� functional� simulation� model.�

�Verilog� HDL� black-box� file� for� the� MegaCore� function� variation.� Use� this� file� when� using�

�a� third-party� EDA� tool� to� synthesize� your� design.�

�Memory� initialization� files� in� INTEL� Hex� format.� These� files� are� required� both� for�

�simulation� with� IP� functional� simulation� models� and� synthesis� using� the� Quartus� II�

�software.�

�A� timing� and� resource� estimation� netlist� for� use� in� some� third-party� synthesis� tools.�

�MATLAB� m-file� describing� a� MATLAB� bit-accurate� model.�

�A� Tcl� script� that� can� be� used� to� assign� NativeLink� simulation� testbench� settings� to� the�

�Quartus� II� project.�

�MATLAB� testbench� file.�

�ModelSim� Waveform� file.�

�Notes� to� Table� 2–1:�

�(1)� <� variation� name� >� is� a� prefix� variation� name� supplied� automatically� by� IP� Toolbench.�

�(2)� The� <� entity� name� >� prefix� is� added� automatically.� The� VHDL� code� for� each� MegaCore� instance� is� generated� dynamically� when� you� click� Finish�

�so� that� the� <� entity� name� >� is� different� for� every� instance.� It� is� generated� from� the� <� variation� name� >� by� appending� _st.�

�November� 2013�

�Altera� Corporation�

�NCO� MegaCore� Function�

�User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| EMM06DRMT-S288 | CONN EDGECARD 12POS .156 EXTEND |

| VLCF4024T-470MR44-2 | INDUCTOR POWER 47UH 0.44A SMD |

| RP10-483.3SE/N | CONV DC/DC 10W 36-75VIN 3.3VOUT |

| M3YYK-2606R | IDC CABLE - MPD26K/MC26M/MPD26K |

| M3RRK-2606R | IDC CABLE - MPR26K/MC26M/MPR26K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPR-NIOS | 功能描述:开发软件 Nios II MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPROBER 520 | 制造商:TTi-Thurlby Thandar Instruments 功能描述:Bulk 制造商:Aim & Thurlby Thandar Instruments 功能描述:PROBE, CURRENT, POSITIONAL, ON PCB TRACK 制造商:Aim & Thurlby Thandar Instruments 功能描述:PROBE, CURRENT, 5MHZ, 2M; Test Probe Ratio:-; Connector Type A:-; Connector Type B:-; Lead Length:2m; Bandwidth:5MHz; SVHC:No SVHC (19-Dec-2012) ;RoHS Compliant: NA |

| IPR-PCI/MT32 | 功能描述:开发软件 PCI 32b MasterTarget MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-PCI/MT64 | 功能描述:开发软件 PCI 64b MasterTarget MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-PCI/T32 | 功能描述:开发软件 PCI 32-bit Target MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。