参数资料

| 型号: | ISL35822IK |

| 厂商: | Intersil |

| 文件页数: | 60/75页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK/DATA RECOVERY 192EBGA-B |

| 标准包装: | 90 |

| 类型: | 时钟和数据恢复(CDR),多路复用器 |

| PLL: | 无 |

| 输入: | CML |

| 输出: | CML,CMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 8:8 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 3.1875Gbps |

| 电源电压: | 1.425 V ~ 1.575 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 192-EBGA |

| 供应商设备封装: | 192-EBGA-B(17x17) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页当前第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页

63

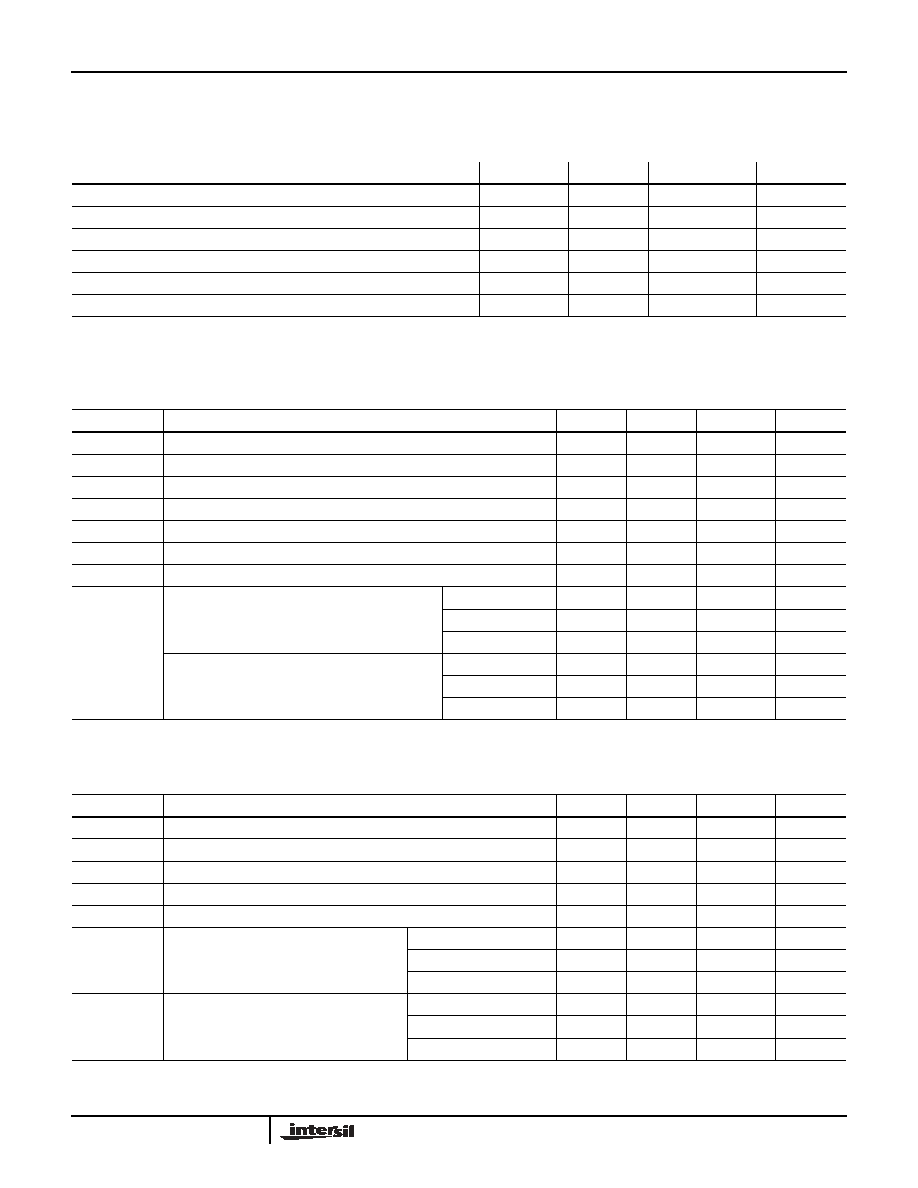

AC and Timing Characteristics

All specifications assume TC = 0°C to +85°C, and VDDAC = VDDAV = VDD = VDDA = 1.5V ± 5% (for the Standard Device) or VDDAC = VDDAV = VDD

= VDDA = 1.35V ± 4%(for the Low Power Device), VDDPR between VDD and 2.5V, unless otherwise specified.

Note (1): System requirements are normally much more restrictive, typically ± 100 ppm. This specification refers to the full reference clock frequency range over which

the ISL35822 will operate.

Note (2): Single-ended peak-to-peak swing.

Note (1): Strictly the 1100 pattern causes a small additional non-random jitter, so that the true random jitter is slightly less than that shown.

Note (2): Parameter is guaranteed by design

Note (1): Jitter specifications include all but 10-12 of the jitter population.

Note (2): Near end driven by ISL35822 Tx without pre-emphasis.

Table 112. REFERENCE CLOCK REQUIREMENTS

SYMBOL

PARAMETER

MIN

TYP

MAX

UNITS

FREF

Ref clock frequency range(1)

124.4

159.375

MHz

FREF

Ref clock frequency offset

-100

+100

ppm

TREFRF

Ref clock Rise and Fall Time

1.5

ns

DTCREF

Ref clock duty cycle

45

50

55

%

VREF

Ref Clock Voltage Swing(2)

300

1000

mV

VCM

Internal Common Mode Voltage

VDD/2

V

Table 113. TRANSMIT SERIAL DIFFERENTIAL OUTPUTS (SEE Figure 9, Figure 10 AND Figure 11)

SYMBOL

PARAMETER

MIN

TYP

MAX

UNIT

TCXnP/N and TXPxP/N output data rate

2.448

3.1875

Gbps

TDR

Differential Rise time (20%-80%)

60

110

130

ps

TDF

Differential Fall time (20%-80%)

60

110

130

ps

TDTOL

Differential Skew Tolerance

TBD

ps

TODS

Lane to Lane Differential Skew (2)

15

ps

Differential Output Impedance

100

Differential Return Loss (to 2.5GHz)

10

dB

TXRJ

Random Jitter (RMS, 1100 pattern)(1)

2.488Gbps

2

4.5

ps

3.125Gbps

2.5

4.5

ps

3.1875

TBD

ps

Total Jitter (RMS, PRBS7 pattern)

2.488Gbps

8

ps

3.125Gbps

6

8

ps

3.1875

8

ps

Table 114. RECEIVE SERIAL DIFFERENTIAL INPUT TIMING REQUIREMENTS (SEE Figure 11)

SYMBOL

PARAMETER

MIN

TYP

MAX

UNITS

RCXnP/N & RXPnP/N Input Data Rate

2.448

3.1875

Gbps

Input Rate deviation from Reference Clock

-200

+200

ppm

Bit Synchronization Time

2500

bits

Frequency Lock after Power-up

2

s

TDTOL

Input Differential Skew

75

ps

TDJ

Deterministic Jitter(1,2)

2.488Gbps

TBD

UI

3.125Gbps

0.7

UI

3.1875

TBD

UI

TJI

Total jitter tolerance

2.488Gbps

TBD

UI

3.125Gbps

0.88

UI

3.1875

TBD

UI

ISL35822

相关PDF资料 |

PDF描述 |

|---|---|

| VI-22Y-MX-S | CONVERTER MOD DC/DC 3.3V 49.5W |

| VI-22Y-MW-S | CONVERTER MOD DC/DC 3.3V 66W |

| MS27474E16B55PA | CONN RCPT 55POS JAM NUT W/PINS |

| V24A24M300BF3 | CONVERTER MOD DC/DC 24V 300W |

| D38999/24KC4SA | CONN RCPT 4POS JAM NUT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL35822LP | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Octal 2.488Gbps to 3.187Gbps/ Lane Retimer |

| ISL35822LPIK | 功能描述:IC CLOCK/DATA RECOVERY 192EBGA-B RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ISL36111 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11.1Gb/s Lane Extender |

| ISL36111DRZ-EVALZ | 功能描述:EVAL BOARD FOR ISL36111DRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板 |

| ISL36111DRZ-T7 | 功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1 |

发布紧急采购,3分钟左右您将得到回复。