参数资料

| 型号: | ISL8120IRZEC |

| 厂商: | Intersil |

| 文件页数: | 22/33页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 32-QFN |

| 标准包装: | 60 |

| PWM 型: | 电压模式 |

| 输出数: | 2 |

| 频率 - 最大: | 1.5MHz |

| 占空比: | 90% |

| 电源电压: | 3 V ~ 22 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 32-VFQFN 裸露焊盘 |

| 包装: | 管件 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

�� �

�

�

�ISL8120IR�

�Functional� Description�

�Initialization�

�Initially,� the� ISL8120IRZEC� Power-On� Reset� (POR)� circuits�

�continually� monitor� the� bias� voltages� (PVCC� and� VCC)� and�

�the� voltage� at� EN� pin.� The� POR� function� initiates� soft-start�

�operation� 384� clock� cycles� after� the� EN� pin� voltage� is� pulled�

�to� be� above� 0.8V,� all� input� supplies� exceed� their� POR�

�thresholds� and� the� PLL� locking� time� expires,� as� shown� in�

�Figure� 4.� The� enable� pin� can� be� used� as� a� voltage� monitor�

�and� to� set� desired� hysteresis� with� an� internal� 30� μ� A� sinking�

�current� going� through� an� external� resistor� divider.� The�

�sinking� current� is� disengaged� after� the� system� is� enabled.�

�This� feature� is� especially� designed� for� applications� that�

�require� higher� input� rail� POR� for� better� undervoltage�

�protection.� For� example,� in� 12V� applications,� R� UP� =� 53.6k�

�and� R� DOWN� =� 5.23k� will� set� the� turn-on� threshold�

�(V� EN_RTH� )� to� 10.6V� and� turn-off� threshold� (V� EN_FTH� )� to� 9V,�

�with� 1.6V� hysteresis� (V� EN_HYS� ).�

�During� shutdown� or� fault� conditions,� the� soft-start� is� reset�

�quickly� while� UGATE� and� LGATE� changes� states� immediately�

�(<100ns)� upon� the� input� drops� below� falling� POR.�

�HIGH� =� ABOVE� POR;� LOW� =� BELOW� POR�

�.�

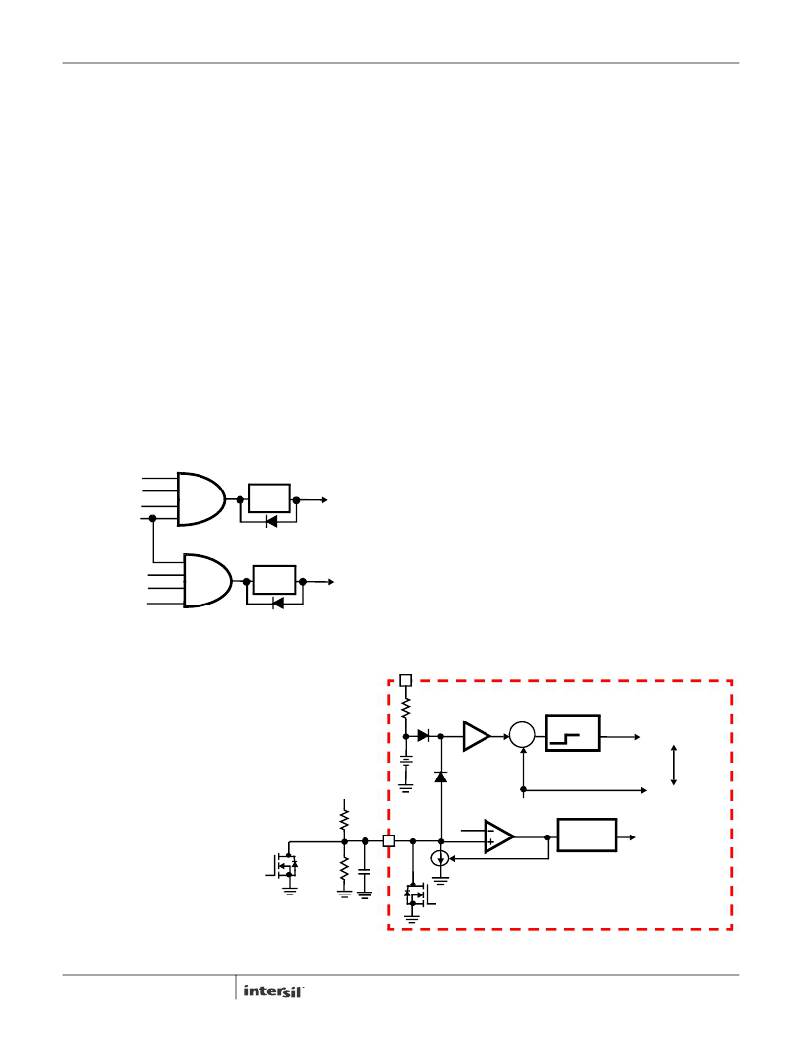

�Voltage� Feed-forward�

�Other� than� used� as� a� voltage� monitor� described� in� previous�

�section,� the� voltages� applied� to� the� EN/FF� pins� are� also� fed�

�to� adjust� the� amplitude� of� each� channel’s� individual�

�sawtooth.� The� amplitude� of� each� channel’s� sawtooth� is� set� to�

�1.25� times� of� the� corresponding� EN/FF� voltage� upon� its�

�enable� (above� 0.8V).� This� helps� to� maintain� a� constant� gain�

�(� G� M� =� VIN� ?� D� MAX� ?� Δ� V� RAMP� )� contributed� by� the� modulator�

�and� the� input� voltage� to� achieve� optimum� loop� response�

�over� a� wide� input� voltage� range.� The� sawtooth� ramp� offset�

�voltage� is� 1V� (equal� to� 0.8V*1.25),� and� the� peak� of� the�

�sawtooth� is� limited� to� VCC� -� 1.4V.� With� VCC� =� 5.4V,� the�

�ramp� has� a� maximum� peak-to-peak� amplitude� of� VCC� -� 2.4V�

�(equal� to� 3V);� So� the� feed-forward� voltage� effective� range� is�

�typically� 3x� as� the� ramp� amplitude� ranges� from� 1V� to� 3V.�

�A� 384� cycle� delay� is� added� after� the� system� reaches� its�

�rising� POR� and� prior� to� the� soft-start.� The� RC� timing� at� the�

�EN/FF� pin� should� be� sufficiently� small� to� ensure� that� the�

�input� bus� reaches� its� static� state� and� the� internal� ramp�

�circuitry� stabilizes� before� soft-start.� A� large� RC� could� cause�

�the� internal� ramp� amplitude� not� to� synchronize� with� the� input�

�bus� voltage� during� output� start-up� or� when� recovering� from�

�faults.� It� is� recommended� to� use� open� drain� or� open� collector�

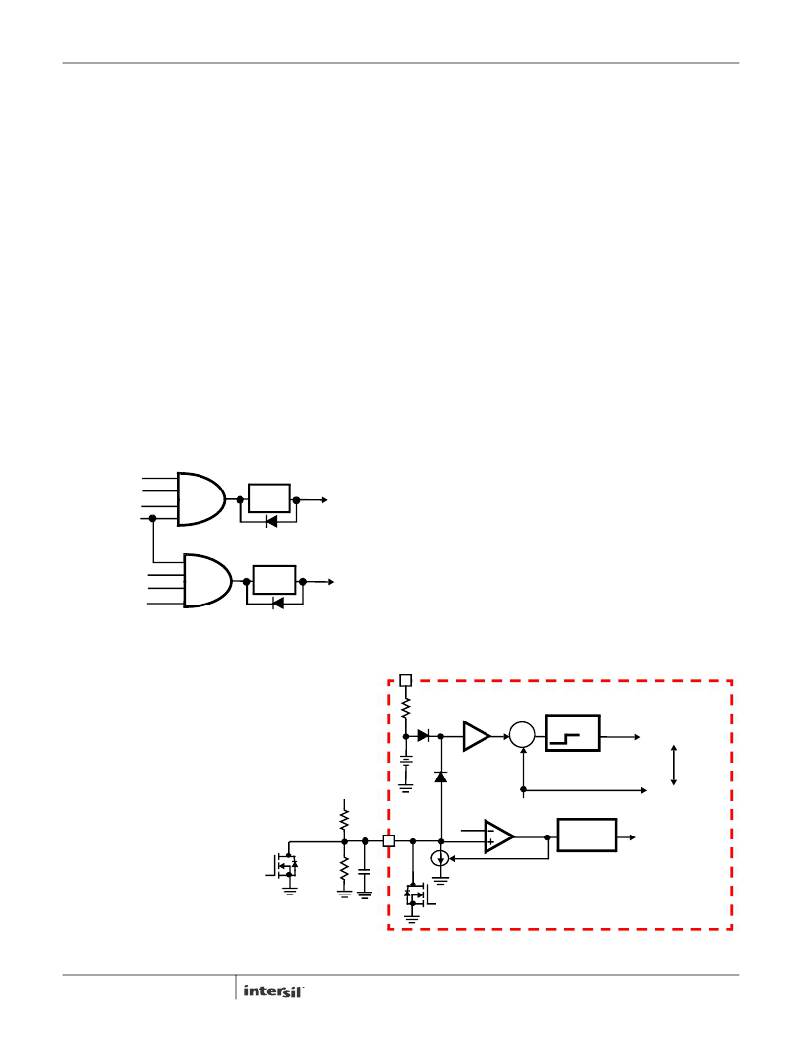

�VCC� POR�

�PVCC� POR�

�EN1/FF1� POR�

�AND�

�384�

�CYCLES�

�SOFT-START�

�OF� CHANNEL� 1�

�to� gate� this� pin� for� any� system� delay,� as� shown� in� Figure� 5.�

�The� multiphase� system� can� immediately� turn� off� all� ICs�

�under� fault� conditions� of� one� or� more� phases� by� pulling� all�

�PLL� LOCKING�

�SOFT-START�

�EN/FF� pins� low.� Thus,� no� bouncing� occurs� among� channels�

�at� fault� and� no� single� phase� could� carry� all� current� and� be�

�over� stressed.�

�VCC� POR�

�PVCC� POR�

�AND�

�384�

�CYCLES�

�OF� CHANNEL� 2�

�EN2/FF2� POR�

�FIGURE� 4.� SOFT-START� INITIALIZATION� LOGIC�

�R� UP� =� -----------------------------�

�R� ?� V�

�EN_REF�

�R� DOWN� =� ---------------------------------------------------------------�

�V� EN_HYS�

�I� EN_HYS�

�UP�

�V� EN_FTH� –� V� EN_REF�

�VCC�

�V� EN_FTH� =� V� EN_RTH� –� V� EN_HYS�

�G� RAMP� =� 1.25�

�VCC� -� 1.4V�

�Δ� V� RAMP� =� LIMIT(V� CC_FF� ×� G� RAMP� ,� VCC� -� 1.4V� -� V� RAMP_OFFSET� )�

�0.8V�

�V� CC_FF�

�∑�

�LIMITER�

�UPPER� LIMIT�

�SAWTOOTH�

�AMPLITUDE�

�(� Δ� V� RAMP� )�

�VIN�

�0.8V�

�V� RAMP_OFFSET� =� 1.0V�

�LOWER� LIMIT�

�(RAMP� OFFSET)�

�SYSTEM� DELAY�

�R� UP�

�R� DOWN�

�EN/FF�

�I� EN_HYS� =� 30� μ� A�

�384� CLOCK�

�CYCLES�

�SOFT-START�

�OV,� OT,� OC,� AND� PLL� LOCKING� FAULTS� (ONLY� FOR� EN/FF1)�

�FIGURE� 5.� SIMPLIFIED� ENABLE� AND� VOLTAGE� FEEDFORWARD� CIRCUIT�

�22�

�FN6763.2�

�November� 11,� 2011�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL8120IRZ | IC REG CTRLR BUCK PWM VM 32-QFN |

| ISL8121IRZ | IC REG CTRLR BUCK PWM VM 24-QFN |

| ISL8126IRZ | IC REG CTRLR BUCK PWM VM 32-QFN |

| ISL8130IAZ | IC REG CTRLR BST FLYBK VM 20QSOP |

| ISL85001IRZ-T | IC REG BUCK ADJ 1A 12DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8120IRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120IRZ-TEC | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120IRZ-TK | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8121 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:3V to 20V, Two-Phase Buck PWM Controller with Integrated 4A MOSFET Drivers |

| ISL8121EVAL1 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:3V to 20V, Two-Phase Buck PWM Controller with Integrated 4A MOSFET Drivers |

发布紧急采购,3分钟左右您将得到回复。