- 您现在的位置:买卖IC网 > PDF目录69017 > M66592WG UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF资料下载

参数资料

| 型号: | M66592WG |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封装: | 0.80 MM PITCH, FBGA-64 |

| 文件页数: | 18/40页 |

| 文件大小: | 1583K |

| 代理商: | M66592WG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

M66592F P/W G

Rev 1.00 2004.10.01 page 25 of 125

2.6 FIFO ports

The transmission and reception buffer memory of the controller uses the FIFO configuration. The FIFO port

registers should be used to access the buffer memory. There are three FIFO ports: the CFIFO port, D0FIFO port, and

D1FIFO port. Each FIFO port is configured of a port register that handles reading of data from the buffer memory, as

well as writing of data to the memory, a selection register used to select the pipe assigned to the FIFO port, a control

register, and registers used specifically for port functions (an SIE register used exclusively for the CFIFO port, and a

transaction counter register used exclusively for the DxFIFO port).

The Notes noted below apply to each of the FIFO ports. For more detailed information, please refer to Chapter 3.4,

Buffer memory.

(1) The DCP buffer memory can only be accessed through the CFIFO port.

(2) Accessing the buffer memory using DMA transfer can be done only through the DxFIFO port.

(3) Accessing the DxFIFO port using the CPU has to be done in conjunction with the functions and restrictions of

the DxFIFO port. (Using the transaction counter, etc.)

(4) When using functions specific to the FIFO port, the selected pipe cannot be changed. (Using the transaction

counter, signal input/output through DMA-related pins, etc.)

(5) Registers corresponding to a FIFO port never affect other FIFO ports.

(6) The same pipe should not be assigned to two or more FIFO ports.

(7) There are two sorts of buffer memory states; the access right is on the CPU side and it is on the SIE side. When

the buffer memory access right is on the SIE side, the memory cannot be properly accessed from the CPU.

(8) The pipe configuration,i.e. PIPECFG, PIPEBUF, PIPEMAXP, PIPEPERI, PIPE1CTR registers of the pipe

selected by the CURPIPE bit should not be changed.

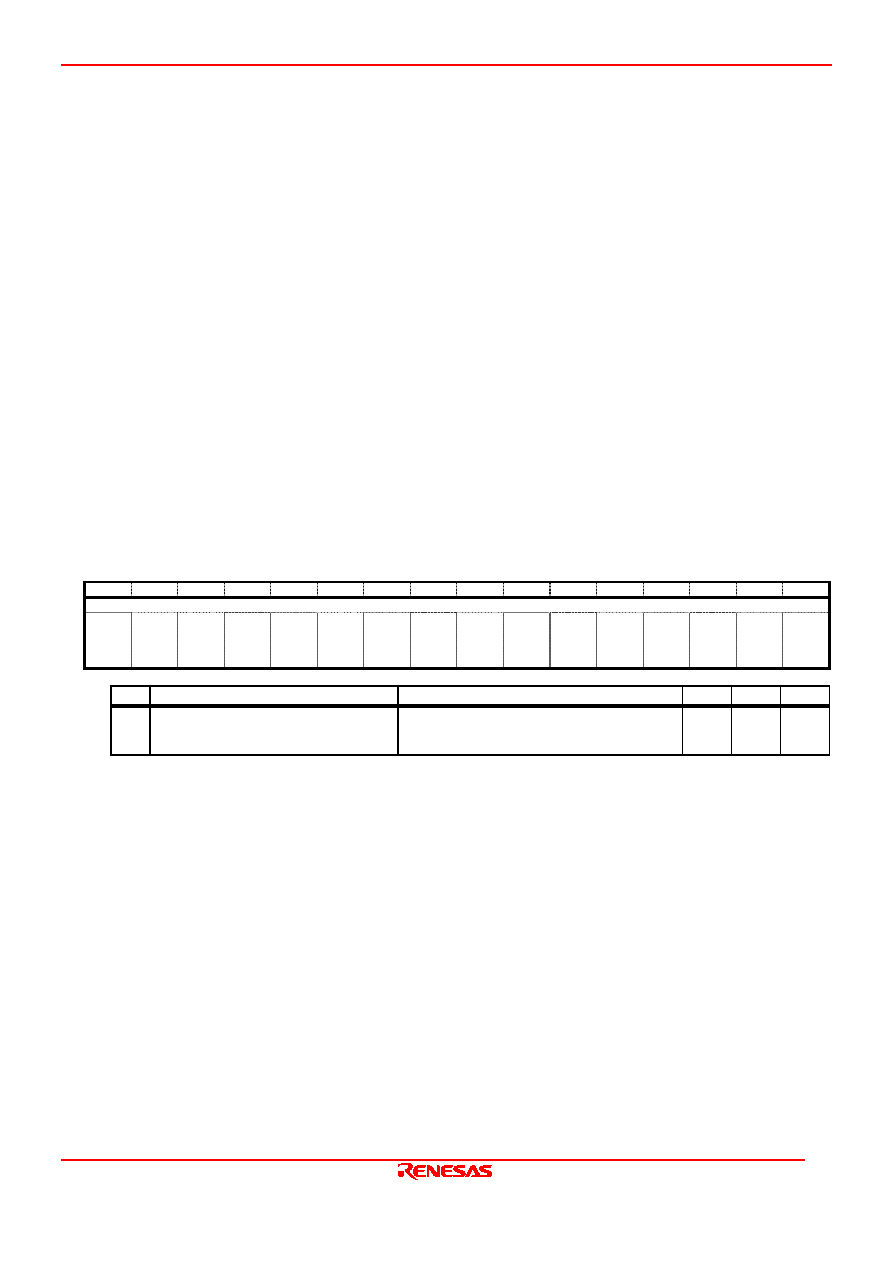

CFIFO port register [CFIFO]

<Address: 10H>

D0FIFO port register [D0FIFO]

<Address: 14H>

D1FIFO port register [D1FIFO]

<Address: 18H>

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

FIFOPORT

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

-

0

Bit

Name

Function

S/W

H/W

Note

15-0 FIFOPORT

FIFO port

This handles reading of received data from the

buffer memory, or writing of the sent data to the

buffer memory.

R/W

3.4

*1)

Note

*1) Only the CFIFO port can be used for DCP access of the buffer memory.

Accessing the buffer memory using DMA transfers can only be done through the D0FIFO and D1FIFO ports.

相关PDF资料 |

PDF描述 |

|---|---|

| M66596FP | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| M68HC11D3CFB1 | 8-BIT, MROM, 1 MHz, MICROCONTROLLER, PQFP44 |

| M68HC711D0CFN | 8-BIT, 2 MHz, MICROCONTROLLER, PQCC44 |

| M68HC711D0CFB | 8-BIT, 2 MHz, MICROCONTROLLER, PQFP44 |

| M68HC711D3CFB1 | 8-BIT, MROM, 1 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M66592WG#RB0Z | 制造商:Renesas Electronics Corporation 功能描述:USB 2 Peripheral Controller 64-Pin FBGA 制造商:Renesas 功能描述:USB 2 Peripheral Controller 64-Pin FBGA |

| M66596FP | 制造商:Renesas Electronics Corporation 功能描述:USB CONTROLLERS |

| M66596FP#RB0Z | 制造商:Renesas Electronics Corporation 功能描述:MCU - Trays 制造商:Renesas Electronics 功能描述:USB Device Controller 64-Pin LQFP Cut Tape 制造商:Renesas Electronics 功能描述:USB Device Controller 64-Pin LQFP Tray 制造商:Renesas 功能描述:USB Device Controller 64-Pin LQFP |

| M66596FPRB0Z | 制造商:Renesas Electronics Corporation 功能描述:USB2.0 Dual Function Controller,LQFP64 |

| M66596WG | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:ASSP (USB2.0 Dual Function Controller) |

发布紧急采购,3分钟左右您将得到回复。