- 您现在的位置:买卖IC网 > PDF目录69017 > M66592WG UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF资料下载

参数资料

| 型号: | M66592WG |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封装: | 0.80 MM PITCH, FBGA-64 |

| 文件页数: | 32/40页 |

| 文件大小: | 1583K |

| 代理商: | M66592WG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页

M66592F P/W G

Rev 1.00 2004.10.01 page 38 of 125

2.10.1 Isochronous errors

With this controller, data transfer errors that occur in isochronous transfers can be confirmed using the OVRN bit

and the CRCE bit of the FRMNUM register. In isochronous transfers, error notification by the NRDY interrupt can be

differentiated using the OVRN bit and the CRCE bit between data buffer errors and packet errors.

Table 2.7and Table 2.8 show the conditions under which the OVRN bit and CRCE bit areset to “1”.

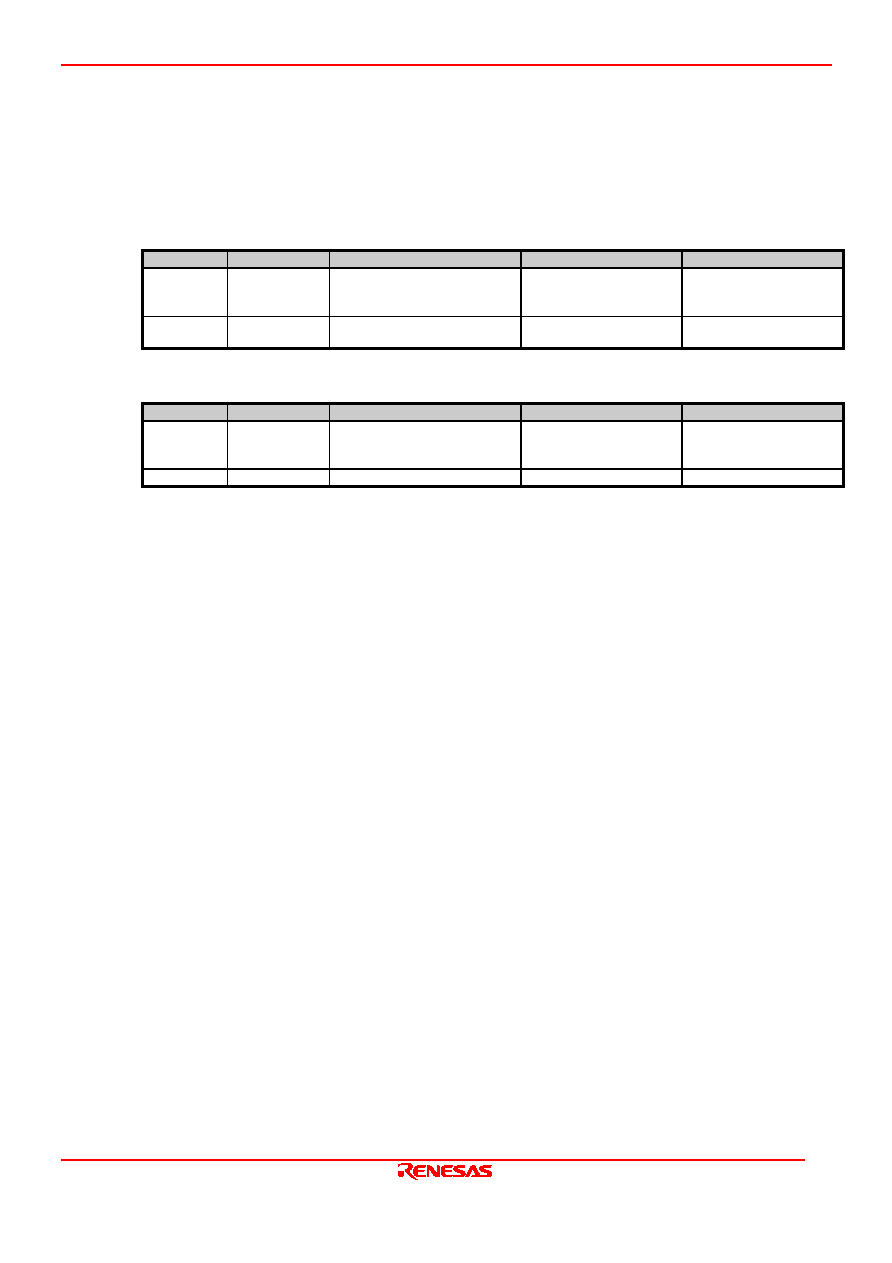

Table 2.7 Error information when an NRDY interrupt is issued in an isochronous out transfer

Bit status

Issued when:

Issue conditions

Detected error

Operation

“OVRN=1"

Data packet is

received

A new data packet is received

before reading of buffer

memory is completed

Reception data buffer

overrun

The new data packet is

thrown out

“CRCE=1"

Data packet is

received

A CRC error, or, a bit stuffing

error is detected

Received packet error

The new data packet is

thrown out

Table 2.8 Error information when an NRDY interrupt is issued in an isochronous in transfer

Bit status

Issued when:

Issue conditions

Detected error

Operation

"OVRN=1"

IN token is

received

An in-token is received before

writing to buffer memory is

completed

Transmission data buffer

underrun

Zero-Length packet

transmission

"CRCE=1"

Not issued

2.10.2 SOF interrupts and frame numbers

The SOFR interrupt operation mode should be selected using the SOFRM bit of the FRMNUM register. Also, the

current frame number can be confirmed using the FRNM bit of the FRMNUM register and the UFRNM bit of the

UFRNUM

register.

With this controller, the frame numbers are refreshed at the timing at which SOF packets are received. If the

controller is unable to detect an SOF packet because the packet has beencorrupted, or for another reason, the FRNM

value is retained until a new SOF packet is received.

At that point, the FRNM bit based on the SOF interpolation timer is not refreshed. Also, the UFRNM bit is

incremented in response to a uSOF packet being received.

相关PDF资料 |

PDF描述 |

|---|---|

| M66596FP | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| M68HC11D3CFB1 | 8-BIT, MROM, 1 MHz, MICROCONTROLLER, PQFP44 |

| M68HC711D0CFN | 8-BIT, 2 MHz, MICROCONTROLLER, PQCC44 |

| M68HC711D0CFB | 8-BIT, 2 MHz, MICROCONTROLLER, PQFP44 |

| M68HC711D3CFB1 | 8-BIT, MROM, 1 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M66592WG#RB0Z | 制造商:Renesas Electronics Corporation 功能描述:USB 2 Peripheral Controller 64-Pin FBGA 制造商:Renesas 功能描述:USB 2 Peripheral Controller 64-Pin FBGA |

| M66596FP | 制造商:Renesas Electronics Corporation 功能描述:USB CONTROLLERS |

| M66596FP#RB0Z | 制造商:Renesas Electronics Corporation 功能描述:MCU - Trays 制造商:Renesas Electronics 功能描述:USB Device Controller 64-Pin LQFP Cut Tape 制造商:Renesas Electronics 功能描述:USB Device Controller 64-Pin LQFP Tray 制造商:Renesas 功能描述:USB Device Controller 64-Pin LQFP |

| M66596FPRB0Z | 制造商:Renesas Electronics Corporation 功能描述:USB2.0 Dual Function Controller,LQFP64 |

| M66596WG | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:ASSP (USB2.0 Dual Function Controller) |

发布紧急采购,3分钟左右您将得到回复。