- 您现在的位置:买卖IC网 > PDF目录80565 > M68LC302CPU20VCT (FREESCALE SEMICONDUCTOR INC) 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | M68LC302CPU20VCT |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 1.40 MM HEIGHT, 0.50 MM PITCH, PLASITC, LQFP-100 |

| 文件页数: | 4/128页 |

| 文件大小: | 641K |

| 代理商: | M68LC302CPU20VCT |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页

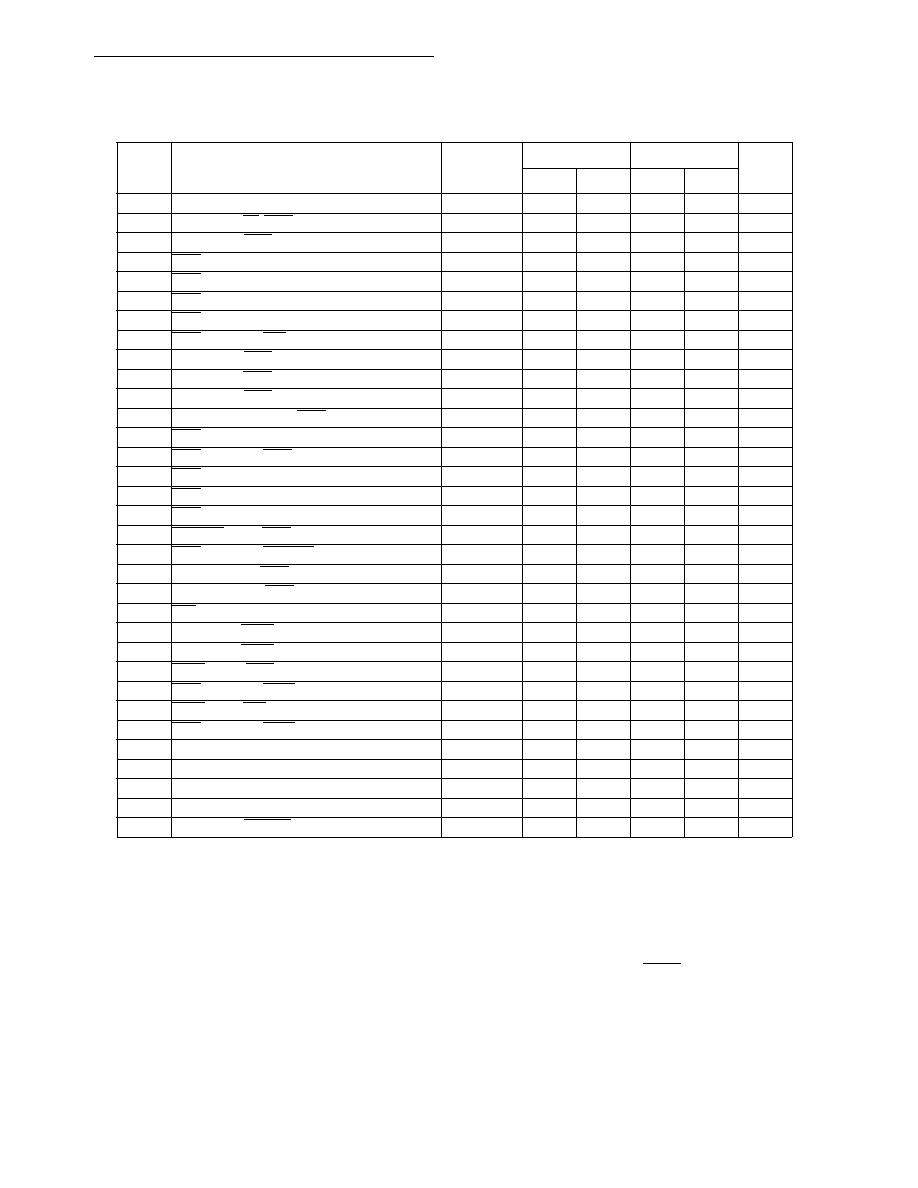

MC68EN302 Electrical Characteristics

8-2

MC68EN302 REFERENCE MANUAL

MOTOROLA

8.3 DRAM INTERFACE TIMING

Any spec numbers shown in diagrams and not listed in the table are unchanged from the

MC68302 User’s Manual.

NOTES:

1. Width increases by clock period (Tcyc) for each wait state added.

2. Width increases by clock period (Tcyc) for each increase in P1–P0 (RAS precharge time).

3. Parity Enabled timing (spec 27A) only applies to bank(s) which have parity enabled.

Table 8-1. DRAM Interface Timing

NUM

CHARACTERISTIC

SYMBOL

20 MHZ

25 MHZ

UNIT

MIN

MAX

MIN

MAX

6A

CLKO Low to Column Address Valid

0

25

0

25

9

CLKO High to AS, RASx Asserted

3

25

3

20

ns

9A

CLKO High to RASx Deasserted

3

25

3

20

ns

400

RASx Asserted to Row Address Invalid

12

-

12

-

ns

401

RASx Asserted to Column Address Valid

15

-

15

-

ns

402

RASx Width Asserted (1)

85

-

75

-

ns

403

RASx Width Negated (2)

85

-

75

-

ns

404

RASx Asserted to CAS Asserted

35

-

35

-

ns

405

CLKO High to CASx Asserted

3

25

3

20

ns

405A

CLKO High to CASx Asserted (Refresh)

3

25

3

20

ns

406

CLKO High to CASx Negated

3

25

3

20

ns

407

Column Address Valid to CASx Asserted

15

-

15

-

ns

408

CASx Asserted to Column Address Negated

50

-

40

-

ns

409

CASx Asserted to RASx Negated

35

-

30

-

ns

410

CASx Width Asserted (1)

75

-

60

-

ns

411

CASx Width Negated (2)

75

-

60

-

ns

412

CASx Negated to Data, Parity-In invalid

0-0-

ns

415

DRAMRW Low to CASx Asserted

30

-

25

-

ns

416

CASx Asserted to DRAMRW High

100

-

80

-

ns

417

Data-Out Valid to CASx Asserted

15

-

10

-

ns

417A

Parity-Out Valid to CASx Asserted

0-0-

ns

418

CAS asserted to Data/Parity-Out Invalid (1)

100

-

80

-

ns

419

CLKO Low to AMUX Negated

3

15

3

15

ns

420

CLKO Low to AMUX Asserted

3

15

3

15

ns

421

AMUX High to RASx Asserted

50

-

40

-

ns

422

RASx Asserted to AMUX Low

10

-

10

-

ns

423

AMUX Low to CAS Asserted

15

-

15

-

ns

424

CASx Asserted to AMUX High

55

-

45

-

ns

23

CLKO Low to Data Out Valid

-

25

-

20

ns

23A

CLKO Low to Parity Out Valid

-

40

-

33

ns

27

Data-In to CLKO Low (Parity Disabled) (3)

6-5-

ns

27A

Data/Parity-In to CLKO Low (Parity Enabled) (3)

16

-

12

-

ns

425

CLKO High to PARITYE Valid

-

15

-

15

ns

相关PDF资料 |

PDF描述 |

|---|---|

| MC68030FE25C | 32-BIT, 25 MHz, MICROPROCESSOR, CQFP132 |

| MC68302CPV16VC | 4 CHANNEL(S), 10M bps, LOCAL AREA NETWORK CONTROLLER, PQFP144 |

| MC68331CFC16B1 | 32-BIT, 16 MHz, MICROCONTROLLER, PQFP132 |

| MC68882CRC16A | 32-BIT, MATH COPROCESSOR, CPGA68 |

| MC68HC11E1VFN3 | 8-BIT, 3 MHz, MICROCONTROLLER, PQCC52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M68LGL061X | 制造商:Panasonic Industrial Company 功能描述:SUB ONLY CRT |

| M68LGL061XA | 制造商:Panasonic Industrial Company 功能描述:CRT OR M68LGL061X |

| M68LNK161X | 制造商:Panasonic Industrial Company 功能描述:CRT |

| M68LUQ085X | 制造商:Panasonic Industrial Company 功能描述:CRT |

| M68LZP195X | 制造商:Panasonic Industrial Company 功能描述:CRT |

发布紧急采购,3分钟左右您将得到回复。