- 您现在的位置:买卖IC网 > PDF目录45226 > MC68HC11C0FN3 (MOTOROLA INC) 8-BIT, 3 MHz, MICROCONTROLLER, PQCC68 PDF资料下载

参数资料

| 型号: | MC68HC11C0FN3 |

| 厂商: | MOTOROLA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 3 MHz, MICROCONTROLLER, PQCC68 |

| 封装: | PLASTIC, LCC-68 |

| 文件页数: | 35/76页 |

| 文件大小: | 394K |

| 代理商: | MC68HC11C0FN3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页当前第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

MOTOROLA

MC68HC11C0

40

MC68HC11C0TS/D

6.1 External Interrupt Requests

The MC68HC11C0 has a total of nine external interrupt inputs. In addition to the two external interrupts

found on other M68HC11 devices (IRQ and XIRQ), seven more inputs for interrupt requests have been

added. The seven additional inputs have been implemented as alternate functions of port F pins. The

interrupt request inputs IRQ[6:0] are individually enabled by bits in the FINTEN register. The IRQ and

XIRQ inputs have been moved and are now alternate functions of port D.

The IRQ and IRQ[6:0] interrupt sources are maskable and share the same priority. These interrupt

sources can be masked globally by bit I in the condition code register as well as locally by enable bits

in control registers. IRQ[6:0] are enabled by bits in the FINTEN register. IRQ is enabled by bits in DIO-

CTL register. Since IRQ[6:0] have the same priority as IRQ, software must poll an interrupt status reg-

ister (FISTAT) to determine the source of the interrupt request. FISTAT is automatically cleared when

it is read by the CPU. FISTAT can be read at any time but cannot be written. Refer to the descriptions

of port F, FINTEN and FISTAT.

When corresponding bits in FINTEN are set, port F lines become interrupt request inputs. Writes to

PORTF drive pins only if the pins are configured for output and corresponding IRQ is disabled.

IS7 is the interrupt status bit for IRQ in port D. FISTAT can be read any time but cannot be written. All

bits are cleared after CPU has read the register following an interrupt request.

IS7 — IRQ Status

0 = No interrupt pending for the corresponding interrupt line

1 = Interrupt pending for the corresponding interrupt line

IS[6:0] — IRQ[6:0] Status

0 = No interrupt pending for the corresponding interrupt line

1 = Interrupt pending for the corresponding interrupt line

The enable bit for IRQ is located in the DIOCTL register.

IE[6:0] — IRQ[6:0] Enable

0 = Interrupt request input is disabled and pin is controlled by DDRF bit

1 = Interrupt request input IRQx is enabled, overriding state of DDRF bit

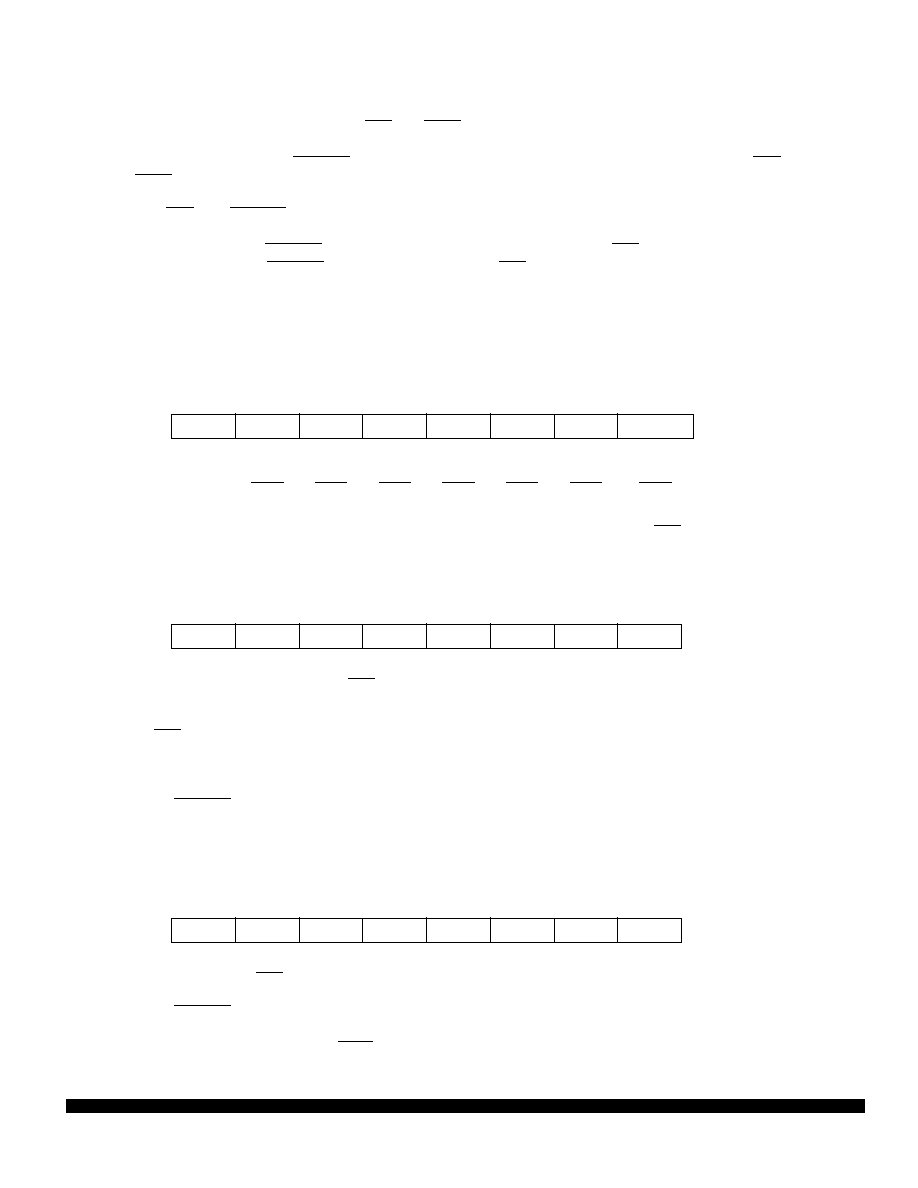

PORTF — Port F Data Register

$0002

Bit 7

654321

Bit 0

—

PF6

PF5

PF4

PF3

PF2

PF1

PF0

RESET:

0000000

0

Alt. Pin

Func.:

—

IRQ6

IRQ5

IRQ4

IRQ3

IRQ2

IRQ1

IRQ0

FISTAT — Port F Interrupt Status

$0004

Bit 7

654321

Bit 0

IS7

IS6

IS5

IS4

IS3

IS2

IS1

IS0

RESET:

00000000

FINTEN — Port F Interrupt Enable

$0005

Bit 7

654321

Bit 0

—

IE6

IE5

IE4

IE3

IE2

IE1

IE0

RESET:

00000000

相关PDF资料 |

PDF描述 |

|---|---|

| MC68HC11D0CFN2 | 8-BIT, 2 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC11D0CFB2 | 8-BIT, 2 MHz, MICROCONTROLLER, PQFP44 |

| MC68HC11D3CFN2 | 8-BIT, MROM, 2 MHz, MICROCONTROLLER, PQCC44 |

| MC68HC711D3CP3 | 8-BIT, OTPROM, 3 MHz, MICROCONTROLLER, PDIP40 |

| MC68HC11D3CFN3 | 8-BIT, MROM, 3 MHz, MICROCONTROLLER, PQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68HC11C0FU3 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11C0MFN2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11C0MFU2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11C0VFN2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontroller |

| MC68HC11C0VFU2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。