- 您现在的位置:买卖IC网 > PDF目录67996 > ML60851CTB (LAPIS SEMICONDUCTOR CO LTD) UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ML60851CTB |

| 厂商: | LAPIS SEMICONDUCTOR CO LTD |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| 封装: | 10 X 10 MM, 0.80 MM PITCH, PLASTIC, TQFP-44 |

| 文件页数: | 6/68页 |

| 文件大小: | 442K |

| 代理商: | ML60851CTB |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

PEDL60851C-02

1Semiconductor

ML60851C

13/67

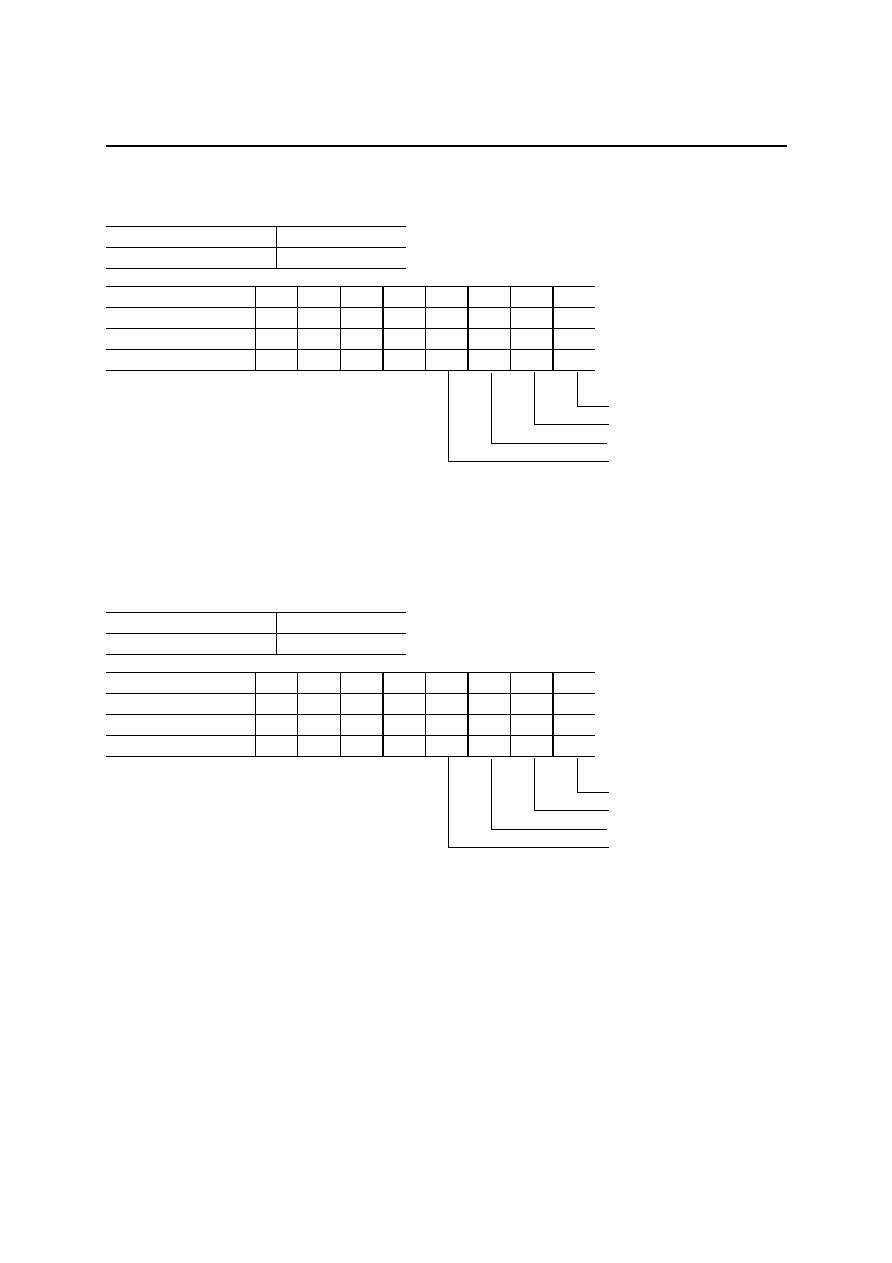

Packet Error Register (PKTERR)

Read address

C2h

Write address

—

D7

D6

D5

D4

D3

D2

D1

D0

After a hardware reset

000

0000

0

After a bus reset

000

0000

0

Definition

0

00

Each bit is asserted when the corresponding error occurs and is deasserted when SOP is received.

This register is used to report the error information. This register is useful for the tests during development, or for

preparing the error frequency measurement report. This register is not particularly required for the specification of

commercial a product.

FIFO Status Register 1 (FIFOSTAT1)

Read address

C3h

Write address

—

D7

D6

D5

D4

D3

D2

D1

D0

After a hardware reset

000

0101

0

After a bus reset

000

0101

0

Definition

0

00

This register reports the statuses of the EP0RXFIFO and the FIFO for EP1. Normally, there is no need to read this

register because it is sufficient to read the packet ready status before reading out or writing in a FIFO.

Receive FIFO0 Full:

This bit becomes “1” when 8-bytes of data are stored in the EP0RXFIFO. This bit is

not set to “1” when a packet less than 8 bytes long (a short packet) is stored in.

Receive FIFO0 Empty: This bit will be “1” when the EP0RXFIFO0 is empty.

FIFO1 Full:

This bit becomes “1” when 64 bytes of data is stored in the FIFO for EP1. This is true

during both transmission and reception. This bit does not become “1” in the case of a

short packet. The FIFO for EP1 has a two-layer structure and can store up to 128

bytes of data. This bit indicates the status of the FIFO in which data being written at

that time. In other words, this bit indicates the status of the FIFO into which the host

computer is writing data when EP1 is receiving data, and of the FIFO into which the

local MCU is writing data when EP1 is transmitting data.

FIFO1 Empty:

This bit becomes “1” when the FIFO for EP1 is empty. This is true during both

transmission and reception. The FIFO for EP1 has a two-layer structure and can store

up to 128 bytes of data. This bit indicates the status of the FIFO which is being read

out at that time.

Bit stuff error (R)

Data CRC error (R)

Address CRC error (R)

PID Error (R)

Receive FIFO0 Full (R)

Receive FIFO0 Empty (R)

FIFO1 Full (R)

FIFO1 Empty (R)

相关PDF资料 |

PDF描述 |

|---|---|

| ML60851CGA | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML60851DGA | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML60851DTB | UNIVERSAL SERIAL BUS CONTROLLER, PQFP44 |

| ML610Q340-XXXMB | 8-BIT, FLASH, 4.2 MHz, RISC MICROCONTROLLER, PDSO30 |

| ML610340-XXXMB | 8-BIT, MROM, 4.2 MHz, RISC MICROCONTROLLER, PDSO30 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ML60851D | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60851E | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60851EGA | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60851ETB | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

| ML60852 | 制造商:OKI 制造商全称:OKI electronic componets 功能描述:USB Device Controller |

发布紧急采购,3分钟左右您将得到回复。