参数资料

| 型号: | PI7C8150BNDIE |

| 厂商: | Pericom |

| 文件页数: | 67/109页 |

| 文件大小: | 0K |

| 描述: | IC PCI-PCI BRIDGE ASYNC 256-PBGA |

| 标准包装: | 90 |

| 系列: | * |

| 应用: | * |

| 接口: | * |

| 电源电压: | * |

| 封装/外壳: | 256-BGA |

| 供应商设备封装: | 256-PBGA(17x17) |

| 包装: | 管件 |

| 安装类型: | 表面贴装 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页

PI7C8150B

ASYNCHRONOUS 2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 60 of 109

April 2009 – Revision 1.08

The SERR_L enable bit must be set in the command register.

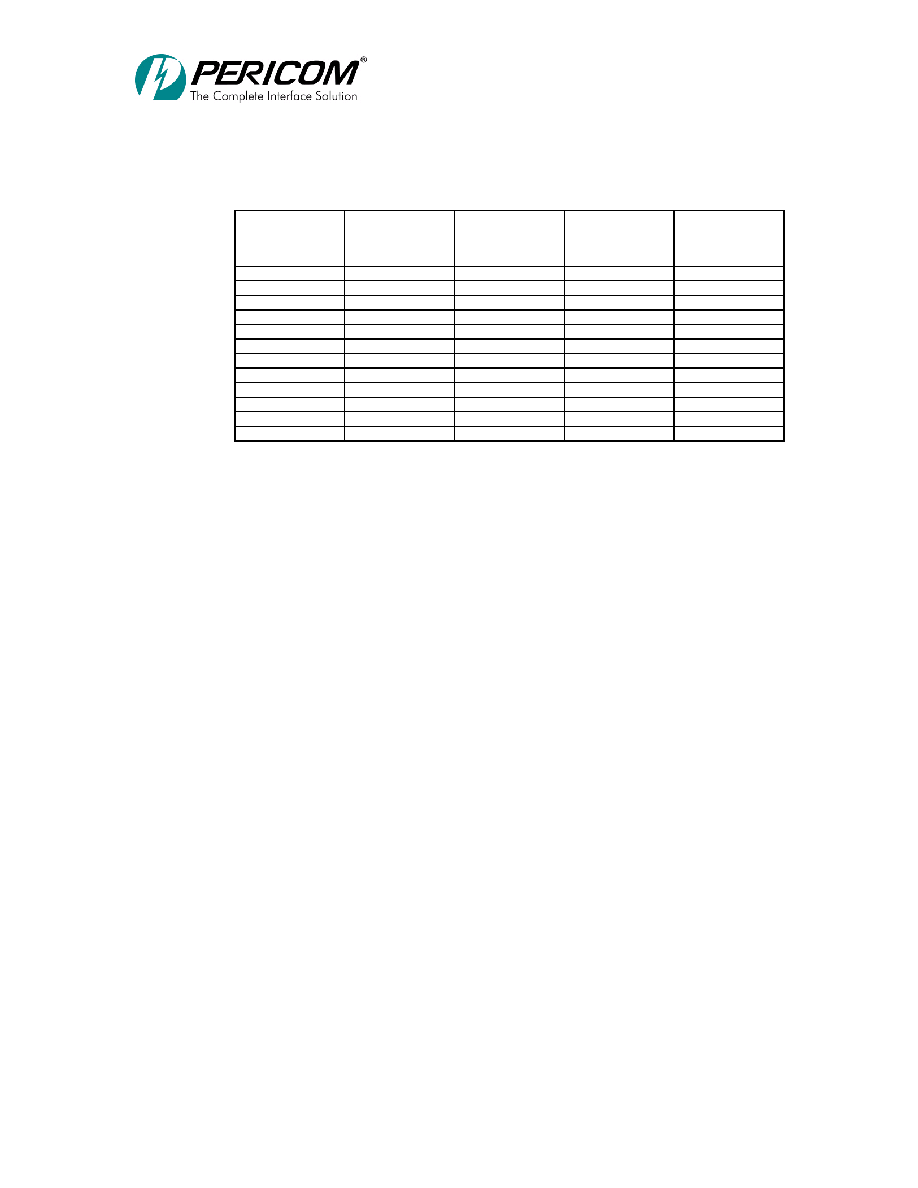

Table 6-7. Assertion of P_SERR_L for Data Parity Errors

P_SERR_L

Transaction Type

Direction

Bus Where Error

Was Detected

Primary /

Secondary Parity

Error Response

Bits

1 (de-asserted)

Read

Downstream

Primary

x / x

1

Read

Downstream

Secondary

x / x

1

Read

Upstream

Primary

x / x

1

Read

Upstream

Secondary

x / x

1

Posted Write

Downstream

Primary

x / x

0

2 (asserted)

Posted Write

Downstream

Secondary

1 / 1

0

3

Posted Write

Upstream

Primary

1 / 1

1

Posted Write

Upstream

Secondary

x / x

1

Delayed Write

Downstream

Primary

x / x

1

Delayed Write

Downstream

Secondary

x / x

1

Delayed Write

Upstream

Primary

x / x

1

Delayed Write

Upstream

Secondary

x / x

X = don’t care

2

The parity error was detected on the target (secondary) bus but not on the initiator (primary) bus.

3

The parity error was detected on the target (primary) bus but not on the initiator (secondary) bus.

6.4

SYSTEM ERROR (SERR_L) REPORTING

PI7C8150B uses the P_SERR_L signal to report conditionally a number of system error

conditions in addition to the special case parity error conditions described in Section 6.2.3.

Whenever assertion of P_SERR_L is discussed in this document, it is assumed that the

following conditions apply:

For PI7C8150B to assert P_SERR_L for any reason, the SERR_L enable bit must be

set in the command register.

Whenever PI7C8150B asserts P_SERR_L, PI7C8150B must also set the signaled

system error bit in the status register.

In compliance with the PCI-to-PCI Bridge Architecture Specification, PI7C8150B asserts

P_SERR_L when it detects the secondary SERR_L input, S_SERR_L, asserted and the

SERR_L forward enable bit is set in the bridge control register. In addition, PI7C8150B

also sets the received system error bit in the secondary status register.

PI7C8150B also conditionally asserts P_SERR_L for any of the following reasons:

Target abort detected during posted write transaction

Master abort detected during posted write transaction

Posted write data discarded after 2

24 (default) attempts to deliver (224 target retries

received)

Parity error reported on target bus during posted write transaction (see previous

section)

相关PDF资料 |

PDF描述 |

|---|---|

| PI7C8152BMAIE | IC PCI-PCI BRIDGE 2PORT 160-MQFP |

| PI7C8154ANAE | IC PCI-PCI BRIDGE ASYNC 304-PBGA |

| PI7C8154BNAIE | IC PCI-PCI BRIDGE ASYNC 304-PBGA |

| PI7C9X110BNBE | IC PCIE TO PCI REV BRG 160LFBGA |

| PI7C9X130DNDE | IC PCIE-PCIX BRIDGE 1PORT 256BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PI7C8150BNDIE-33 | 功能描述:外围驱动器与原件 - PCI 2 Port 32B PCI Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| PI7C8150DMAE | 功能描述:外围驱动器与原件 - PCI 2-Port PCI Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| PI7C8150DND | 制造商:Pericom Semiconductor Corporation 功能描述:BRIDGE 制造商:Pericom Semiconductor Corporation 功能描述:2 PORT PCI BRIDGE - Rail/Tube |

| PI7C8150DNDE | 功能描述:外围驱动器与原件 - PCI 2-Port PCI Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| PI7C8150EVB | 功能描述:界面开发工具 2 Port PCI Bridge Eval Brd RoHS:否 制造商:Bourns 产品:Evaluation Boards 类型:RS-485 工具用于评估:ADM3485E 接口类型:RS-485 工作电源电压:3.3 V |

发布紧急采购,3分钟左右您将得到回复。