- 您现在的位置:买卖IC网 > PDF目录268241 > PIC17CXX (Microchip Technology Inc.) EPROM Memory Programming Specification PDF资料下载

参数资料

| 型号: | PIC17CXX |

| 厂商: | Microchip Technology Inc. |

| 英文描述: | EPROM Memory Programming Specification |

| 中文描述: | EPROM存储器编程规范 |

| 文件页数: | 37/71页 |

| 文件大小: | 1173K |

| 代理商: | PIC17CXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页

PIC17C4X

DS30412C-page 42

1996 Microchip Technology Inc.

6.8

Bank Select Register (BSR)

The BSR is used to switch between banks in the data

memory

area

In

the

PIC17C42,

PIC17CR42, and PIC17C42A only the lower nibble is

implemented. While in the PIC17C43, PIC17CR43,

and PIC17C44 devices, the entire byte is implemented.

The lower nibble is used to select the peripheral regis-

ter bank. The upper nibble is used to select the general

purpose memory bank.

All the Special Function Registers (SFRs) are mapped

into the data memory space. In order to accommodate

the large number of registers, a banking scheme has

been used. A segment of the SFRs, from address 10h

to address 17h, is banked. The lower nibble of the bank

select register (BSR) selects the currently active

“peripheral bank.” Effort has been made to group the

peripheral registers of related functionality in one bank.

However, it will still be necessary to switch from bank

to bank in order to address all peripherals related to a

single task. To assist this, a MOVLB bank instruction is

in the instruction set.

For the PIC17C43, PIC17CR43, and PIC17C44

devices, the need for a large general purpose memory

space dictated a general purpose RAM banking

scheme. The upper nibble of the BSR selects the cur-

rently active general purpose RAM bank. To assist this,

a MOVLR bank instruction has been provided in the

instruction set.

If the currently selected bank is not implemented (such

as Bank 13), any read will read all '0's. Any write is com-

pleted to the bit bucket and the ALU status bits will be

set/cleared as appropriate.

Note:

Registers in Bank 15 in the Special Func-

tion

Register

area,

are

reserved

for

Microchip use. Reading of registers in this

bank may cause random values to be read.

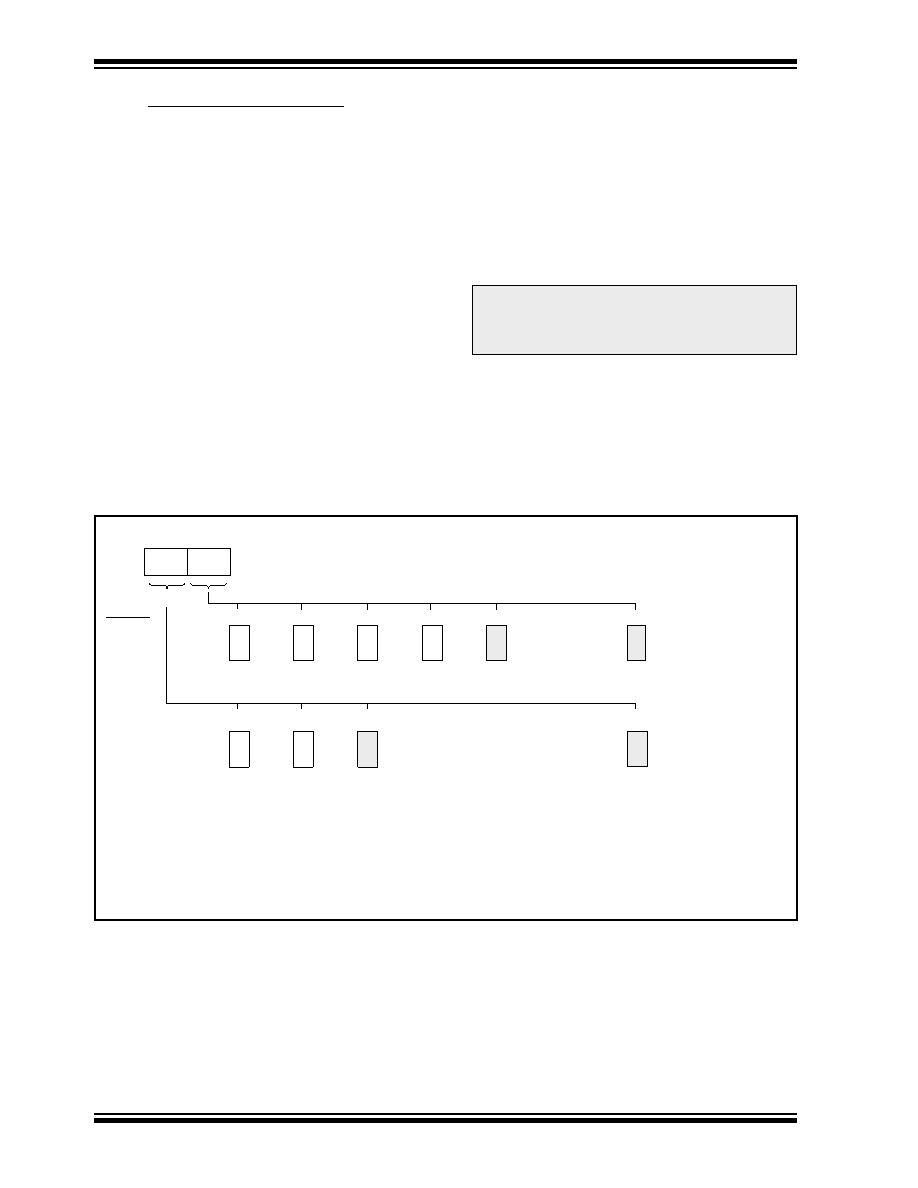

FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

74 3

0

10h

17h

BSR

01

2

3

4

15

20h

FFh

(1)

(2)

Bank 15

Bank 4

Bank 3

Bank 2

Bank 1

Bank 0

01

2

Bank 2

Bank 1

Bank 0

15

Bank 15

SFR

Banks

GPR

Banks

Address

Range

Note 1:

Only Banks 0 through Bank 3 are implemented. Selection of an unimplemented bank is not recommended.

Bank 15 is reserved for Microchip use, reading of registers in this bank may cause random values to be read.

2:

Only Banks 0 and Bank 1 are implemented. Selection of an unimplemented bank is not recommended.

相关PDF资料 |

PDF描述 |

|---|---|

| PALCE16V8Z-25JC | EE CMOS Zero-Power 20-Pin Universal Programmable Array Logic |

| PALCE16V8Z-25JI | EE CMOS Zero-Power 20-Pin Universal Programmable Array Logic |

| PALCE16V8Z-25PC | EE CMOS Zero-Power 20-Pin Universal Programmable Array Logic |

| PALCE16V8Z-25PI | EE CMOS Zero-Power 20-Pin Universal Programmable Array Logic |

| PALCE16V8Z-25SC | EE CMOS Zero-Power 20-Pin Universal Programmable Array Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC17LC42A-08/L | 功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC17LC42A-08/P | 功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC17LC42A-08/PQ | 功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC17LC42A-08/PT | 功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC17LC42A-08I/L | 功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。