- 您现在的位置:买卖IC网 > PDF目录378056 > PM73488-PI (PMC-SIERRA INC) 5 Gbit/s ATM Switch Fabric Element PDF资料下载

参数资料

| 型号: | PM73488-PI |

| 厂商: | PMC-SIERRA INC |

| 元件分类: | 数字传输电路 |

| 英文描述: | 5 Gbit/s ATM Switch Fabric Element |

| 中文描述: | ATM SWITCHING CIRCUIT, PBGA596 |

| 封装: | EPBGA-596 |

| 文件页数: | 41/135页 |

| 文件大小: | 1735K |

| 代理商: | PM73488-PI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页

PMC-Sierra, Inc.

PM73488 QSE

L

PMC-980616

Issue 3

5 Gbit/s ATMSwitch Fabric Element

Released

Datasheet

43

The information bits encoding is described in Table 7.

3.2

The data acknowledge signals (BP_ACK_IN and BP_ACK_OUT) are used to indicate if, at the current cell time, a

cell was successfully transmitted or not. Data acknowledge is a single line per port that returns from a cell’s destina-

tion in the reverse direction from the data flow. If the cell is being blocked by the switch, this information is gener-

ated directly by the QSE. If the cell is not being blocked by the switch, this information is forwarded from the next

switch stage.

Data Acknowledge

The data acknowledge signal provides the following information to the QRT:

The cell was successfully received by the QRT at the cell destination (ACK).

The cell was not accepted by the QRT at the cell destination (does not happen by design in the PM73487).

The cell was blocked by the switch at the output of the switch fabric (refer to

section 9.3.30

“ACK_PAYLOAD” on page 109

).

The cell was blocked internal to the switch fabric (refer to

section 9.3.30 “ACK_PAYLOAD” on page 109

).

The cell was detected as a parity error cell by a QSE (refer to

section 9.3.30 “ACK_PAYLOAD” on

page 109

).

The cell was headed to a gang of which all ports are dead (refer to

section 9.3.31

“GANG_DEAD_ACK_PAYLOAD” on page 110

).

Thus, direct information is provided to the QRT on a per-cell basis and on a per-VC basis.

The QSE behavior to support the above scenario is as follows:

If the cell was a parity errored cell, and the QSE is configured to check parity in the CHIP_MODE register

(refer to the field labeled

“PARITY_CHECK” on page 95

), then the parity acknowledge in the

ACK_PAYLOAD register is sent (the default is ONACK).

If the cell is dropped due to congestion at an output of the QSE, then Ack Payload for cells dropped due to

congestion in the ACK_PAYLOAD register is sent (bits3:0). Refer to bits 3:0 in

section 9.3.31

“GANG_DEAD_ACK_PAYLOAD” on page 110

.

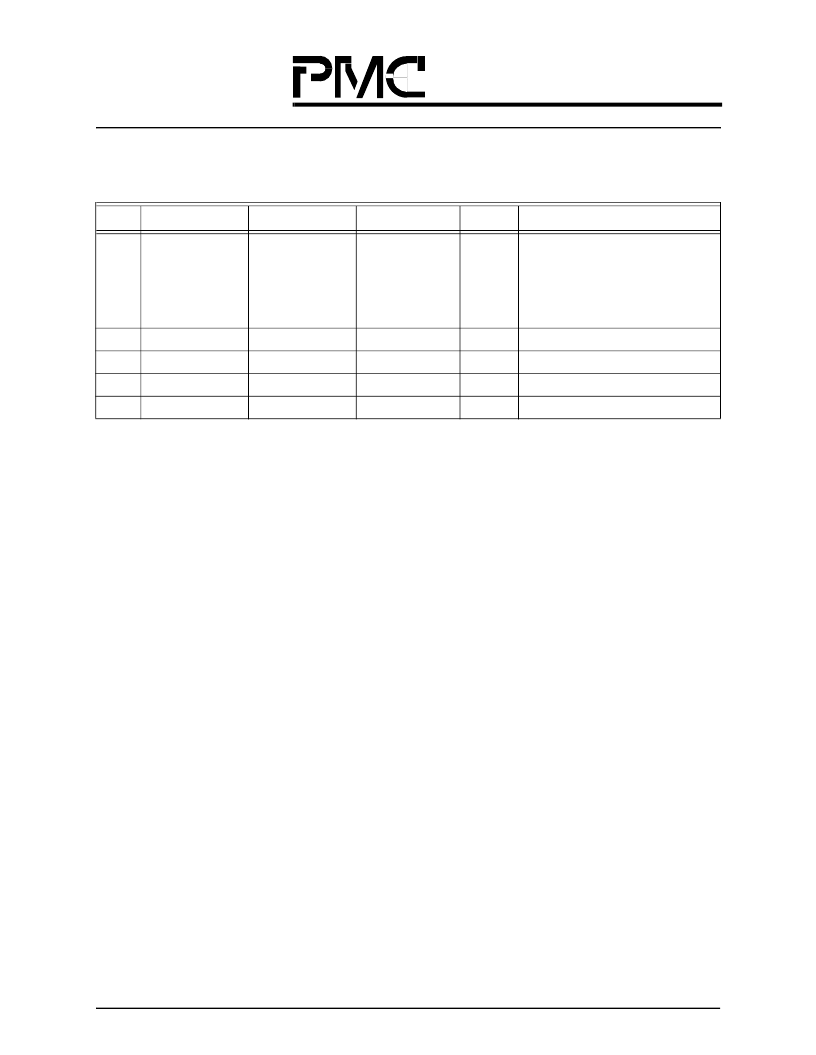

Table 7. Information Bit Encoding

Mode

Data 3

Data 2

Data 1

Data 0

Description

0

1 = Backpressure

on high-priority

multicast cell.

1 = Backpressure

on medium-priority

multicast cell.

1 = Backpressure

on low-priority

multicast cell.

0

Backpressure information.

This signal is present each cell time

regardless of whether a cell was

transmitted or not (on that link).

This signal is withheld if any problem

is detected on the input port.

1

0

0

0

0

Unassigned.

1

0

1

0

0

Signals MNACK.

1

1

0

0

0

Signals ONACK.

1

1

1

0

0

Signals ACK.

相关PDF资料 |

PDF描述 |

|---|---|

| PM73488 | 5 Gbit/s ATM Switch Fabric Element |

| PM7349 | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| PM7350 | Dual Serial Link, PHY Multiplexer |

| PM7350-PI | DUAL SERIAL LINK PHY MULTIPLEXER |

| PM7351 | OCTAL SERIAL LINK MULTIPLEXER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PM7349 | 制造商:PMC 制造商全称:PMC 功能描述:Quad J2, E3 and DS-3 Framer |

| PM7349-BI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| PM7350 | 制造商:PMC 制造商全称:PMC 功能描述:DUAL SERIAL LINK PHY MULTIPLEXER |

发布紧急采购,3分钟左右您将得到回复。