- 您现在的位置:买卖IC网 > PDF目录134951 > Q80C32-30SHXXX:RD (TEMIC SEMICONDUCTORS) 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 PDF资料下载

参数资料

| 型号: | Q80C32-30SHXXX:RD |

| 厂商: | TEMIC SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 30 MHz, MICROCONTROLLER, CQFP44 |

| 文件页数: | 76/83页 |

| 文件大小: | 8336K |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页

88

7707F–AVR–11/10

AT90USB82/162

13. Timer/Counter0 and Timer/Counter1 Prescalers

Timer/Counter0 and 1 share the same prescaler module, but the Timer/Counters can have dif-

ferent prescaler settings. The description below applies to all Timer/Counters. Tn is used as a

general name, n = 0 or 1.

13.0.1

Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This

provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system

clock frequency (f

CLK_I/O). Alternatively, one of four taps from the prescaler can be used as a

clock source. The prescaled clock has a frequency of either f

CLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256, or

f

CLK_I/O/1024.

13.0.2

Prescaler Reset

The prescaler is free running, i.e., operates independently of the Clock Select logic of the

Timer/Counter, and it is shared by the Timer/Counter Tn. Since the prescaler is not affected by

the Timer/Counter’s clock select, the state of the prescaler will have implications for situations

where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is

enabled and clocked by the prescaler (6 > CSn2:0 > 1). The number of system clock cycles from

when the timer is enabled to the first count occurs can be from 1 to N+1 system clock cycles,

where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the prescaler reset for synchronizing the Timer/Counter to program execu-

tion. However, care must be taken if the other Timer/Counter that shares the same prescaler

also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is

connected to.

13.0.3

External Clock Source

An external clock source applied to the Tn pin can be used as Timer/Counter clock (clk

Tn). The

Tn pin is sampled once every system clock cycle by the pin synchronization logic. The synchro-

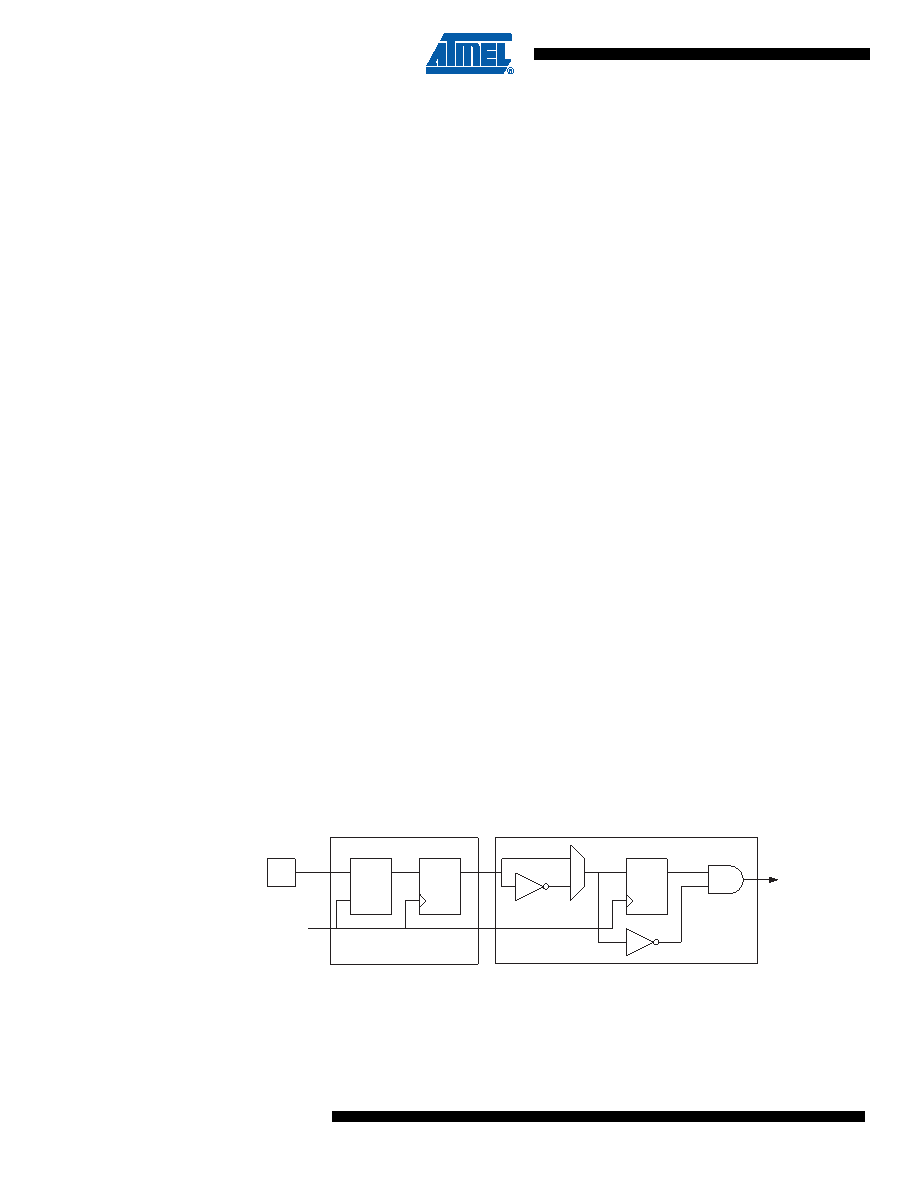

nized (sampled) signal is then passed through the edge detector. Figure 13-1 shows a functional

equivalent block diagram of the Tn synchronization and edge detector logic. The registers are

clocked at the positive edge of the internal system clock (clk

I/O). The latch is transparent in the

high period of the internal system clock.

The edge detector generates one clk

Tn pulse for each positive (CSn2:0 = 7) or negative (CSn2:0

= 6) edge it detects.

Figure 13-1. Tn/T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles

from an edge has been applied to the Tn pin to the counter is updated.

Enabling and disabling of the clock input must be done when Tn has been stable for at least one

system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated.

Tn_sync

(To Clock

Select Logic)

Edge Detector

Synchronization

DQ

LE

DQ

Tn

clk

I/O

相关PDF资料 |

PDF描述 |

|---|---|

| Q80C32-36:R | 8-BIT, 36 MHz, MICROCONTROLLER, CQFP44 |

| Q80C32-36SHXXX:R | 8-BIT, 36 MHz, MICROCONTROLLER, CQFP44 |

| Q80C32-42:D | 8-BIT, 42 MHz, MICROCONTROLLER, CQFP44 |

| Q80C32-42:R | 8-BIT, 42 MHz, MICROCONTROLLER, CQFP44 |

| Q80C32-42SHXXX:D | 8-BIT, 42 MHz, MICROCONTROLLER, CQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| Q80N-5 | 制造商:POWERBOX 制造商全称:Powerbox 功能描述:0.5 WATTS - 100 - 10KV SINGLE OUTPUT DC/DC INDUSTRIAL |

| Q-810 | 功能描述:交流电源插头和插座 NEMA L5-15P LOCKING DEVICE RoHS:否 制造商:Hirose Connector 产品:Plugs 系列: 电流额定值:3 A 电压额定值:30 V 安装角:Straight 安装风格:Cable 颜色: 端口数量: |

| Q81022511000000 | 制造商:Epson Electronics America Inc 功能描述:TF2-J4DB1 184.3200MHZ |

| Q811 | 制造商:Captive Fastener Corporation 功能描述: |

| Q-812 | 制造商:Qualtek Electronics Corporation 功能描述:NEMA TWIST-LOCK 制造商:Qualtek Electronics Corporation 功能描述:Nema St Blade Twist Lock |

发布紧急采购,3分钟左右您将得到回复。