- 您现在的位置:买卖IC网 > PDF目录69323 > RM5261A-300H (PMC-SIERRA INC) 64-BIT, 300 MHz, MICROPROCESSOR, PQFP208 PDF资料下载

参数资料

| 型号: | RM5261A-300H |

| 厂商: | PMC-SIERRA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 300 MHz, MICROPROCESSOR, PQFP208 |

| 封装: | HEAT SPREADER, MQFP-208 |

| 文件页数: | 17/42页 |

| 文件大小: | 898K |

| 代理商: | RM5261A-300H |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

24

Document ID: PMC-2002240, Issue 1

RM5261A Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

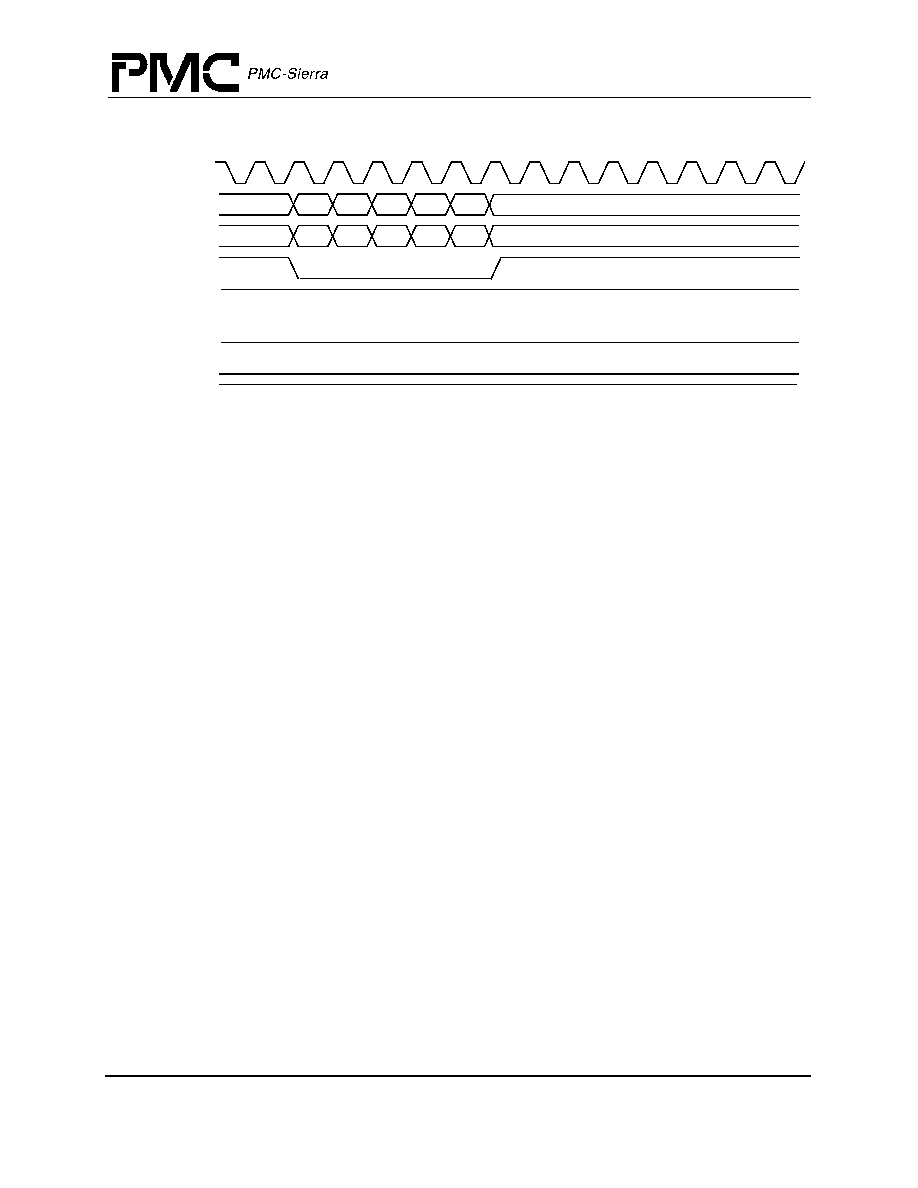

Figure 8

Processor Block Write

3.26 Enhanced Write Modes

The RM5261A implements two enhancements to the original R4000 write mechanism: Write

Reissue and Pipeline Writes. The original R4000 allowed a write address cycle on the SysAD bus

only once every four SysClock cycles. Hence for a non-block write, this meant that two out of

every four cycles were wait states.

Pipelined write mode eliminates these two wait states by allowing the processor to drive a new

write address onto the bus immediately after the previous write data cycle. This allows for higher

SysAD bus utilization. However, at high bus frequencies the processor may drive a subsequent

write onto the bus prior to the time the external agent deasserts WrRdy*, indicating that it can not

accept another write cycle. This can cause the write cycle to be missed.

Write reissue mode is an enhancement to pipelined write mode and allows the processor to reissue

missed write cycles. If WrRdy* is deasserted during the issue phase of a write operation, the cycle

is aborted by the processor and reissued at a later time.

In write reissue mode, a write rate of one write every two bus cycles can be achieved. Pipelined

writes have the same two bus cycle write repeat rate, but can issue one additional write following

the deassertion of WrRdy*.

3.27 External Requests

The External Request pin, ExtRqst*, is asserted by the external agent when it requires mastership

of the system interface, either to perform an independent transfer or to write to the interrupt

register within the RM5261A. An independent transfer is a data transfer between two external

agents or between an external agent and memory or peripheral on the system interface. Following

the asserting of the ExtRqst*, the RM5261A tri-states its drivers allowing the external agent to

use the system interface buses to complete an independent transfer. The external agent is

responsible for returning mastership of the system interface to the RM5261A when it has

completed the independent transfer and does so by executing an External Null cycle.

SysClock

SysAD

SysCmd

ValidOut*

ValidIn*

RdRdy*

WrRdy*

Release*

Addr

Data0

Data1

Data2

Data3

Write

NData

NEOD

相关PDF资料 |

PDF描述 |

|---|---|

| RM54AC163SEA | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, CDIP16 |

| RM54ACT175VFA | ACT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, CDFP16 |

| RM7965A-900UI | 64-BIT, 900 MHz, MICROPROCESSOR, PBGA256 |

| RN80532KC0371M | 1900 MHz, MICROPROCESSOR, CPGA603 |

| RN80532KC0411M | 2000 MHz, MICROPROCESSOR, CPGA603 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RM5261A-300HI-B002 | 制造商:PMC Sierra from Components Direct 功能描述:MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHNOLOGY - Trays 制造商:PMC-Sierra 功能描述:PMC SIERRA RM5261A-300HI-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin MQFP |

| RM5261A-300J-B002 | 制造商:PMC Sierra from Components Direct 功能描述:RM5261A-300J-B002, MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHN - Trays 制造商:PMC SIERRA 功能描述:PMC SIERRA RM5261A-300J-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin LFMQFP |

| RM5270-150S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

| RM5270-200S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

| RM5271-200S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

发布紧急采购,3分钟左右您将得到回复。