- 您现在的位置:买卖IC网 > PDF目录69323 > RM5261A-300H (PMC-SIERRA INC) 64-BIT, 300 MHz, MICROPROCESSOR, PQFP208 PDF资料下载

参数资料

| 型号: | RM5261A-300H |

| 厂商: | PMC-SIERRA INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 300 MHz, MICROPROCESSOR, PQFP208 |

| 封装: | HEAT SPREADER, MQFP-208 |

| 文件页数: | 3/42页 |

| 文件大小: | 898K |

| 代理商: | RM5261A-300H |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

Proprietary and Confidential to PMC-Sierra, Inc and for its Customer’s Internal Use

11

Document ID: PMC-2002240, Issue 1

RM5261A Microprocessor with 64-Bit System Bus Data Sheet

Preliminary

3

Hardware Overview

The RM5261A offers a high-level of integration targeted at high-performance embedded

applications. The key elements of the RM5261A are briefly described below.

3.1

Superscalar Dispatch

The RM5261A has an asymmetric superscalar dispatch unit which allows it to issue an integer

instruction and a floating-point computation instruction simultaneously. Integer instructions

include alu, branch, load/store, and floating-point load/store, while floating-point computation

instructions include floating-point add, subtract, combined multiply-add, and convert. In

combination with its high-throughput fully pipelined floating-point execution unit, the superscalar

capability of the RM5261A provides unparalleled price/performance in computationally intensive

embedded applications.

3.2

CPU Registers

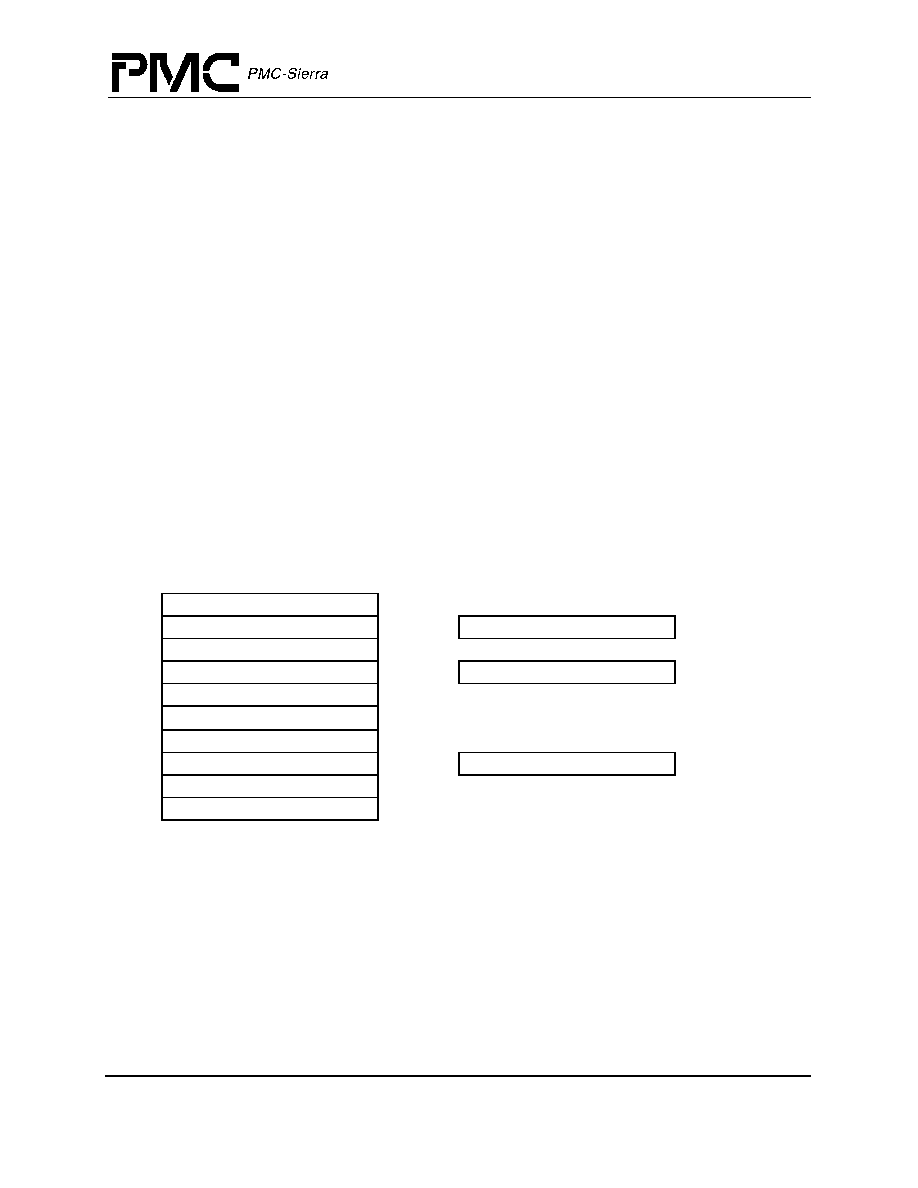

The RM5261A CPU contains 32 general purpose registers, two special purpose registers for

integer multiplication and division, a program counter, and no condition code bits. Figure 2 shows

the user visible state.

Figure 2 CPU Registers

3.3

Integer Unit

The RM5261A implements the MIPS IV Instruction Set Architecture and is therefore fully upward

compatible with applications that run on processors implementing the earlier generation MIPS I-

III instruction sets. Additionally, the RM5261A includes two implementation specific instructions

not found in the baseline MIPS IV ISA but that are useful in the embedded market place. These

instructions are integer multiply-accumulate (MAD) and 3-operand integer multiply (MUL).

The RM5261A integer unit includes thirty-two general purpose 64-bit registers, a load/store

architecture with single cycle ALU operations (add, sub, logical, shift) and an autonomous

multiply/divide unit. Additional register resources include: the HI/LO result registers for the two-

operand integer multiply/divide operations, and the program counter (PC).

General Purpose Registers

63

0

Multiply/Divide Registers

0

63

0

r1

HI

r2

63

0

LO

Program Counter

63

0

r29

PC

r30

r31

相关PDF资料 |

PDF描述 |

|---|---|

| RM54AC163SEA | AC SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, CDIP16 |

| RM54ACT175VFA | ACT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, CDFP16 |

| RM7965A-900UI | 64-BIT, 900 MHz, MICROPROCESSOR, PBGA256 |

| RN80532KC0371M | 1900 MHz, MICROPROCESSOR, CPGA603 |

| RN80532KC0411M | 2000 MHz, MICROPROCESSOR, CPGA603 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RM5261A-300HI-B002 | 制造商:PMC Sierra from Components Direct 功能描述:MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHNOLOGY - Trays 制造商:PMC-Sierra 功能描述:PMC SIERRA RM5261A-300HI-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin MQFP |

| RM5261A-300J-B002 | 制造商:PMC Sierra from Components Direct 功能描述:RM5261A-300J-B002, MICROPROCESSOR 64-BIT 300MHZ 0.18UM TECHN - Trays 制造商:PMC SIERRA 功能描述:PMC SIERRA RM5261A-300J-B002, Microprocessor 64-Bit 300MHz 0.18um Technology 3.3V 208-Pin LFMQFP |

| RM5270-150S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

| RM5270-200S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

| RM5271-200S | 制造商:未知厂家 制造商全称:未知厂家 功能描述:64-Bit Microprocessor |

发布紧急采购,3分钟左右您将得到回复。