- 您现在的位置:买卖IC网 > PDF目录225148 > SC9RS08KA1J3CDB (FREESCALE SEMICONDUCTOR INC) 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO6 PDF资料下载

参数资料

| 型号: | SC9RS08KA1J3CDB |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDSO6 |

| 封装: | 3 X 3 MM, 0.80 MM HEIGHT, ROHS COMPLIANT, DFN-6 |

| 文件页数: | 3/134页 |

| 文件大小: | 3114K |

| 代理商: | SC9RS08KA1J3CDB |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页

Chapter 12 Development Support

SC9RS08KA2 Series Data Sheet, Rev. 1

100

Freescale Semiconductor

The BDC serial communication protocol requires the host to know the target BDC clock speed.

Commands and data are sent most significant bit first (MSB-first) at 16 BDC clock cycles per bit. The

interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC

command that was in progress when this timeout occurs is aborted without affecting the memory or

operating mode of the target MCU system.

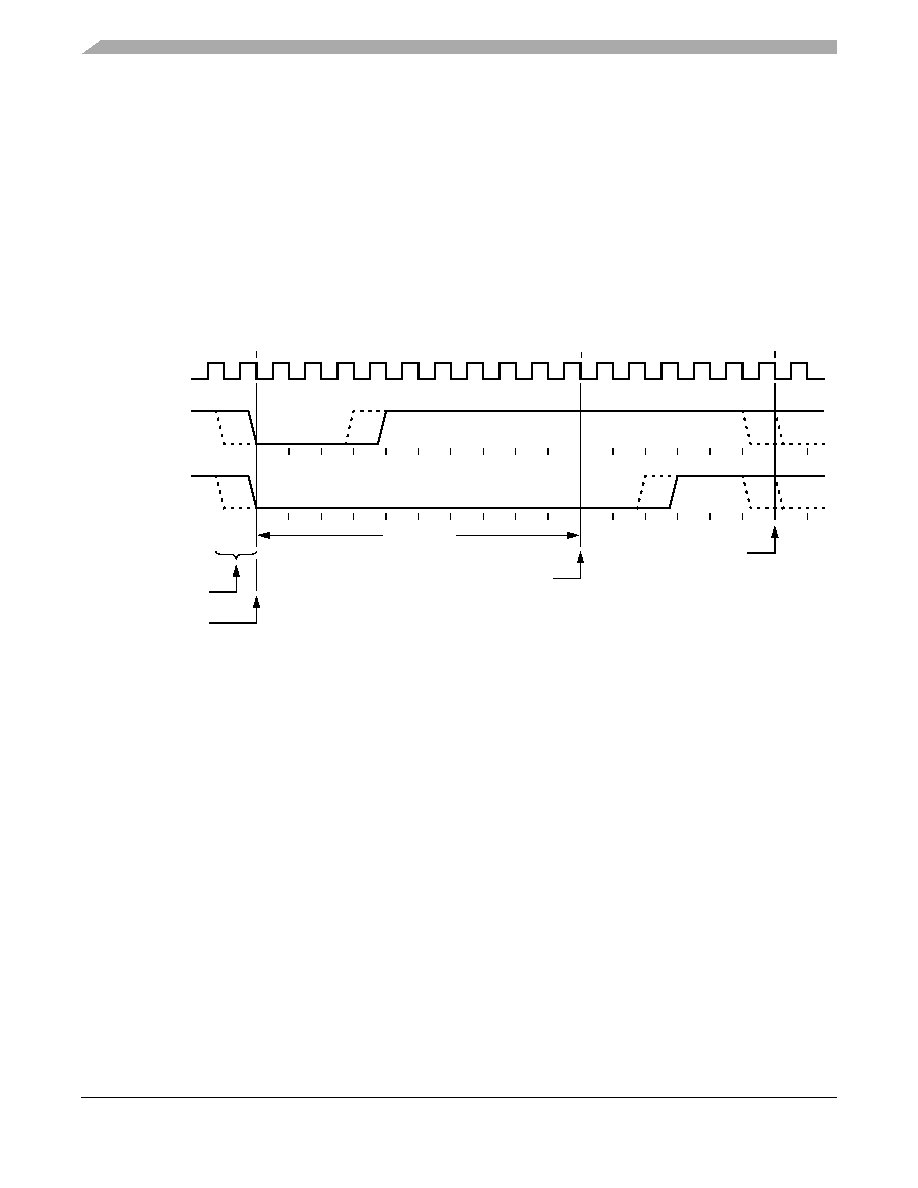

Figure 12-3 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target MCU. The host

is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where

the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the

bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during

host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin

during the host-to-target period, there is no need to treat the line as an open-drain signal during this period.

Figure 12-3. BDC Host-to-Target Serial Bit Timing

Figure 12-4 shows the host receiving a logic 1 from the target MCU. Because the host is asynchronous to

the target, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived

start of the bit time in the target. The host holds the BKGD pin low long enough for the target to recognize

it (at least two target BDC cycles). The host must release the low drive before the target drives a brief

active-high speedup pulse seven cycles after the perceived start of the bit time. The host must sample the

bit level approximately 10 cycles after it started the bit time.

EARLIEST START

TARGET SENSES BIT LEVEL

10 CYCLES

SYNCHRONIZATION

UNCERTAINTY

BDC CLOCK

(TARGET MCU)

HOST

TRANSMIT 1

HOST

TRANSMIT 0

PERCEIVED START

OF BIT TIME

OF NEXT BIT

相关PDF资料 |

PDF描述 |

|---|---|

| SCA-6 | 0 MHz - 3000 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| SCA1N3595US | 0.125 A, 125 V, SILICON, SIGNAL DIODE |

| SCD0705T-6R8M-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| SCD0705T-6R8L-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| SCD0705T-6R8K-N | 1 ELEMENT, 6.8 uH, FERRITE-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SC9RS08KA1J3CPC | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA1J3CSC | 制造商:Freescale Semiconductor 功能描述:8-BIT RS08 CISC 1KB FLASH 2.5V/3.3V/5V 8-PIN SOIC N RAIL - Rail/Tube 制造商:Freescale Semiconductor 功能描述:1K FLASH W/ ACMP 62 RAM |

| SC9RS08KA2 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA2J3CDB | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

| SC9RS08KA2J3CPC | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:RS08 Microcontrollers |

发布紧急采购,3分钟左右您将得到回复。