- 您现在的位置:买卖IC网 > PDF目录231502 > W3E32M72S-266BC (WHITE ELECTRONIC DESIGNS CORP) 32M X 72 DDR DRAM, 0.75 ns, PBGA219 PDF资料下载

参数资料

| 型号: | W3E32M72S-266BC |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 32M X 72 DDR DRAM, 0.75 ns, PBGA219 |

| 封装: | 32 X 25 MM, PLASTIC, BGA-219 |

| 文件页数: | 19/19页 |

| 文件大小: | 739K |

| 代理商: | W3E32M72S-266BC |

W3E32M72S-XBX

9

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

March 2006

Rev. 2

White Electronic Designs Corp. reserves the right to change products or specications without notice.

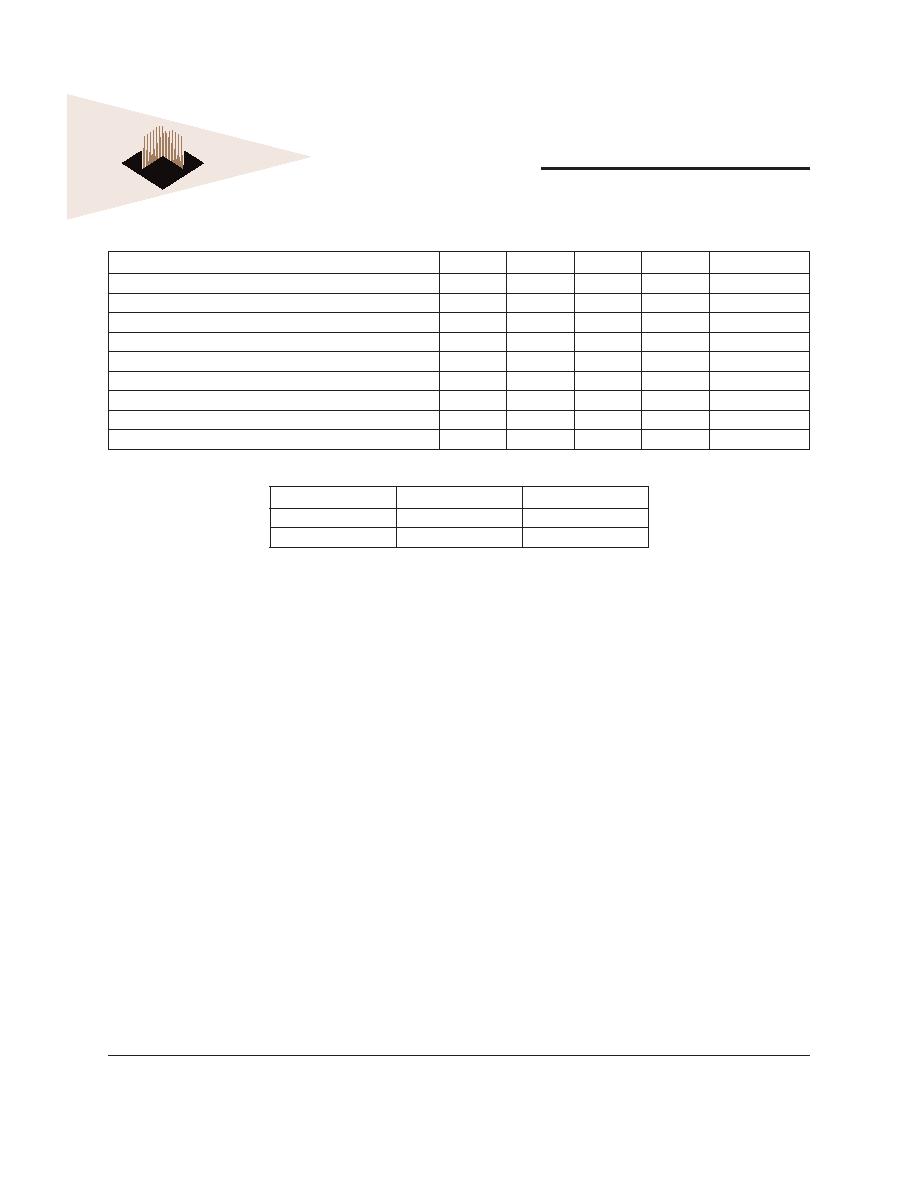

TRUTH TABLE – COMMANDS (NOTE 1)

NOTES:

1.

CKE is HIGH for all commands shown except SELF REFRESH.

2.

A0-12 dene the op-code to be written to the selected Mode Register. BA0, BA1

select either the mode register (0, 0) or the extended mode register (1, 0).

3.

A0-12 provide row address, and BA0, BA1 provide bank address.

4.

A0-9 provide column address; A10 HIGH enables the auto precharge feature (non

persistent), while A10 LOW disables the auto precharge feature; BA0, BA1 provide

bank address.

5.

A10 LOW: BA0, BA1 determine the bank being precharged. A10 HIGH: All banks

precharged and BA0, BA1 are “Don’t Care.”

NAME (FUNCTION)

CS#

RAS#

CAS#

WE#

ADDR

DESELECT (NOP) (9)

H

X

NO OPERATION (NOP) (9)

L

H

X

ACTIVE (Select bank and activate row) ( 3)

L

H

Bank/Row

READ (Select bank and column, and start READ burst) (4)

L

H

L

H

Bank/Col

WRITE (Select bank and column, and start WRITE burst) (4)

L

H

L

Bank/Col

BURST TERMINATE (8)

L

H

L

X

PRECHARGE (Deactivate row in bank or banks) ( 5)

L

H

L

Code

AUTO REFRESH or SELF REFRESH (Enterselfrefreshmode) (6, 7)

L

H

X

LOAD MODE REGISTER (2)

L

Op-Code

TRUTH TABLE – DM OPERATION

NAME (FUNCTION)

DM

DQs

WRITE ENABLE (10)

L

Valid

WRITE INHIBIT (10)

H

X

6.

This command is AUTO REFRESH if CKE is HIGH; SELF REFRESH if CKE is

LOW.

7.

Internal refresh counter controls row addressing; all inputs and I/Os are “Don’t

Care” except for CKE.

8.

Applies only to read bursts with auto precharge disabled; this command is

undened (and should not be used) for READ bursts with auto precharge enabled

and for WRITE bursts.

9.

DESELECT and NOP are functionally interchangeable.

10. Used to mask write data; provided coincident with the corresponding data.

during an AUTO REFRESH command. Each DDR SDRAM

requires AUTO REFRESH cycles at an average interval

of 7.8125μs (maximum).

To allow for improved efficiency in scheduling and

switching between tasks, some exibility in the absolute

refresh interval is provided. A maximum of eight AUTO

REFRESH commands can be posted to any given DDR

SDRAM, meaning that the maximum absolute interval

between any AUTO REFRESH command and the next

AUTO REFRESH command is 9 x 7.8125μs (70.3μs). This

maximum absolute interval is to allow future support for

DLL updates internal to the DDR SDRAM to be restricted

to AUTO REFRESH cycles, without allowing excessive

drift in tAC between updates.

Although not a JEDEC requirement, to provide for future

functionality features, CKE must be active (High) during

the AUTO REFRESH period. The AUTO REFRESH period

begins when the AUTO REFRESH command is registered

and ends tRFC later.

SELF REFRESH*

The SELF REFRESH command can be used to retain

data in the DDR SDRAM, even if the rest of the system is

powered down. When in the self refresh mode, the DDR

SDRAM retains data without external clocking. The SELF

REFRESH command is initiated like an AUTO REFRESH

command except CKE is disabled (LOW). The DLL is

automatically disabled upon entering SELF REFRESH and

is automatically enabled upon exiting SELF REFRESH (A

DLL reset and 200 clock cycles must then occur before a

READ command can be issued). Input signals except CKE

are “Don’t Care” during SELF REFRESH. VREF voltage is

also required for the full duration of SELF REFRESH.

The procedure for exiting self refresh requires a sequence

of commands. First, CK and CK# must be stable prior

to CKE going back HIGH. Once CKE is HIGH, the DDR

SDRAM must have NOP commands issued for tXSNR,

because time is required for the completion of any internal

refresh in progress.

相关PDF资料 |

PDF描述 |

|---|---|

| W3HG128M72AEF665F1MCG | DDR DRAM MODULE, DMA240 |

| WS128K32-100G4QE | 512K X 8 MULTI DEVICE SRAM MODULE, 100 ns, CQFP68 |

| WS128K32N-70HME | 512K X 8 MULTI DEVICE SRAM MODULE, 70 ns, CHIP66 |

| WPS512K32-15PJI | 2M X 8 MULTI DEVICE SRAM MODULE, 15 ns, PQMA68 |

| WMD4M4V-80F2M | 4M X 4 FAST PAGE DRAM, 80 ns, CDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W3E32M72S-266BI | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 266 MHZ, 219 PBGA, INDUSTRIAL TEMP. - Bulk |

| W3E32M72S-266BM | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 266 MHZ, 219 PBGA, MIL-TEMP. - Bulk |

| W3E32M72S-266SBC | 制造商:Microsemi Corporation 功能描述:32M X 72 DDR, 2.5V, 266 MHZ, 208 PBGA, COMMERCIAL TEMP. - Bulk |

| W3E32M72S-266SBI | 制造商:White Electronic Designs 功能描述:32M X 72 DDR, 2.5V, 266 MHZ, 208 PBGA, IND TEMP CUSTOM - Bulk 制造商:Microsemi Corporation 功能描述:SDRAM MEMORY |

| W3E32M72S-266SBM | 制造商:WEDC 制造商全称:White Electronic Designs Corporation 功能描述:32Mx72 DDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。