- 您现在的位置:买卖IC网 > PDF目录276857 > WEDPND16M72S-266BC (WHITE ELECTRONIC DESIGNS CORP) 16M X 72 DDR DRAM, 0.75 ns, PBGA219 PDF资料下载

参数资料

| 型号: | WEDPND16M72S-266BC |

| 厂商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分类: | DRAM |

| 英文描述: | 16M X 72 DDR DRAM, 0.75 ns, PBGA219 |

| 封装: | 32 X 25 MM, PLASTIC, BGA-219 |

| 文件页数: | 14/16页 |

| 文件大小: | 441K |

| 代理商: | WEDPND16M72S-266BC |

7

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

WEDPND16M72S-XBX

The DESELECT function (CS HiGH) prevents new commands

from being executed by the DDR SDRAM. The SDRAM is

effectively deselected. Operations already in progress are

not affected.

The NO OPERATION (NOP) command is used to perform a

NOP to the selected DDR SDRAM (CS is LOW). This prevents

unwanted commands from being registered during idle or

wait states. Operations already in progress are not affected.

The Mode Registers are loaded via inputs A0-12. The LOAD

MODE REGISTER command can only be issued when all

banks are idle, and a subsequent executable command

cannot be issued until tMRD is met.

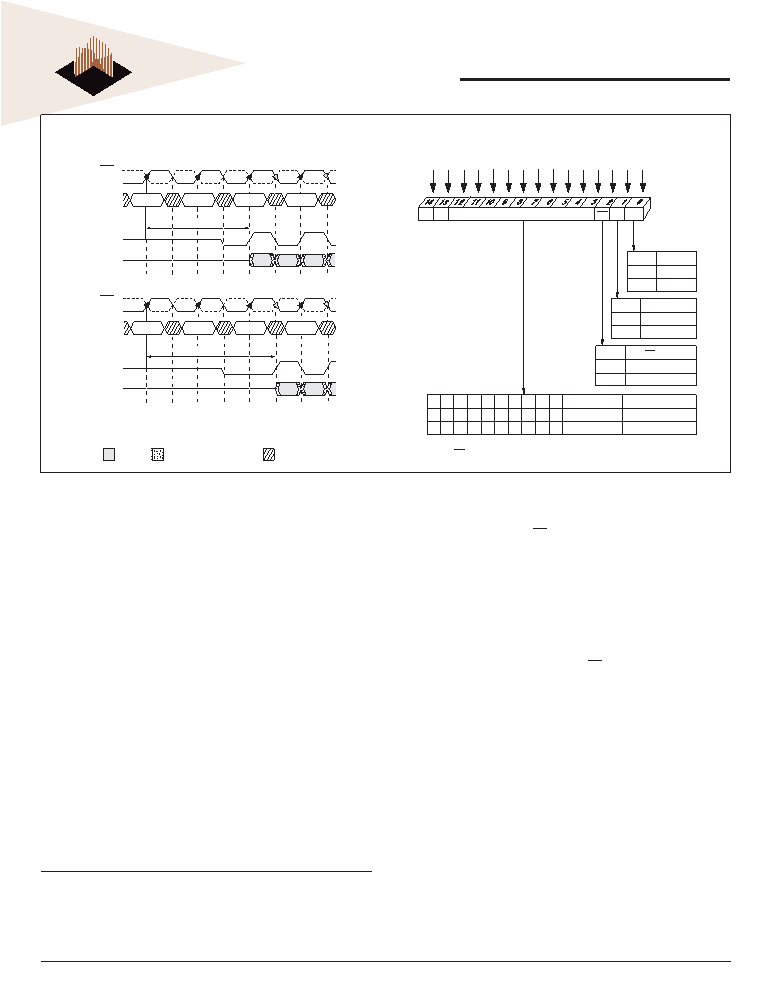

COMMAND

READ

NOP

CL = 2.5

DON'T CARE

TRANSITIONING DATA

DQ

DQS

T0

T1

T2

T2n

T3

T3n

COMMAND

READ

NOP

CL = 2

DQ

DQS

CLK

T0

T1

T2

T2n

T3

T3n

Burst Length = 4 in the cases shown

Shown with nominal tAC and nominal tDSDQ

DATA

CLK

The normal full drive strength for all outputs are specified to

be SSTL2, Class II. The DDR SDRAM suppor ts an option for

reduced drive. This option is intended for the suppor t of

the lighter load and/or point-to-point environments. The

selection of the reduced drive strength will alter the DQs

and DQSs from SSTL2, Class II drive strength to a reduced

drive strength, which is approximately 54 percent of the

SSTL2, Class II drive strength.

The DLL must be enabled for normal operation. DLL enable

is required during power-up initialization and upon return-

ing to normal operation after having disabled the DLL for the

purpose of debug or evaluation. (When the device exits

self refresh mode, the DLL is enabled automatically.) Any

time the DLL is enabled, 200 clock cycles must occur be-

fore a READ command can be issued.

FIG. 4 CAS LATENCY

FIG. 5 EXTENDED MODE REGISTER DEFINITION

OUTPUT DRIVE STRENGTH

DLL ENABLE/DISABLE

The Tr uth Table provides a quick reference of available

commands. This is followed by a written description of

each command.

COMMANDS

NO OPERATION (NOP)

DESELECT

LOAD MODE REGISTER

DLL

Enable

Disable

DLL

DS

A9

A7

A6

A5

A4

A3

A8

A2

A1

A0

Extended Mode

Register (Ex)

Address Bus

Operating Mode

A10

A11

11

01

BA0

BA1

QFC

E0

0

1

Drive Strength

Normal

Reduced

E1

0

1

QFC Function

Disabled

Reserved

E22

0

-

Operating Mode

Reserved

E2, E1, E0

Valid

-

E12

0

-

E10

0

-

E9

0

-

E8

0

-

E7

0

-

E6

0

-

E5

0

-

E4

0

-

E3

0

-

A12

E11

0

-

1. E14 and E13 must be "0, 1" to select the Extended Mode Register (vs. the base Mode Register)

2. The QFE function is not supported.

相关PDF资料 |

PDF描述 |

|---|---|

| WMS512K8-20FFIA | 512K X 8 STANDARD SRAM, 20 ns, DFP32 |

| WMS512K8-17FQA | 512K X 8 STANDARD SRAM, 17 ns, CDFP36 |

| WMS512K8-20CLQ | 512K X 8 STANDARD SRAM, 20 ns, CQCC32 |

| WMS512K8-45DEQA | 512K X 8 STANDARD SRAM, 45 ns, CDSO32 |

| WED3DG7266V10D1-SG | 64M X 72 SYNCHRONOUS DRAM MODULE, ZMA144 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| WEDPNF8M721V-1010BC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8Mx72 Synchronous DRAM + 8Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M721V-1010BI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8Mx72 Synchronous DRAM + 8Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M721V-1010BM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8Mx72 Synchronous DRAM + 8Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M721V-1012BC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8Mx72 Synchronous DRAM + 8Mb Flash Mixed Module Multi-Chip Package |

| WEDPNF8M721V-1012BI | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8Mx72 Synchronous DRAM + 8Mb Flash Mixed Module Multi-Chip Package |

发布紧急采购,3分钟左右您将得到回复。