参数资料

| 型号: | X45620V20I-2.7 |

| 厂商: | Intersil |

| 文件页数: | 16/20页 |

| 文件大小: | 0K |

| 描述: | IC VOLT MON DUAL SW EEPR 20TSSOP |

| 标准包装: | 75 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 75 ms |

| 电压 - 阀值: | 1.75V,2.62V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

�� �

�

�

�X45620�

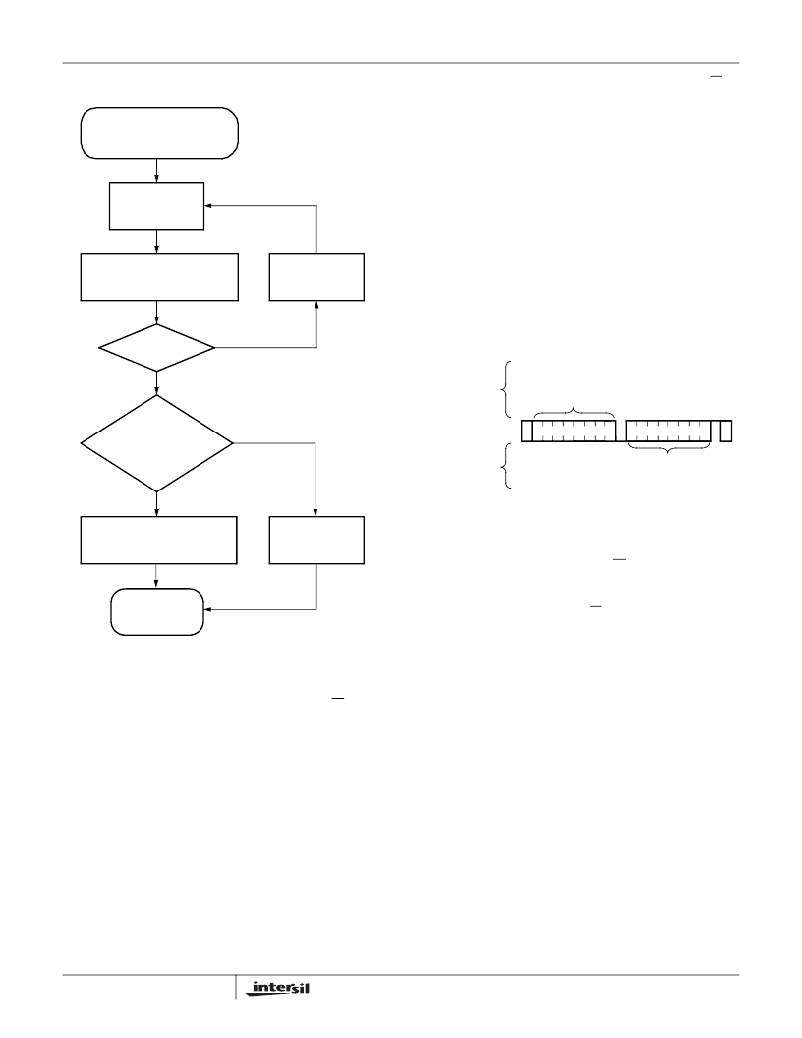

�Figure� 13.� Acknowledge� Polling� Sequence�

�Byte� Load� Completed�

�by� Issuing� Stop.�

�Enter� ACK� Polling�

�Issue�

�Start�

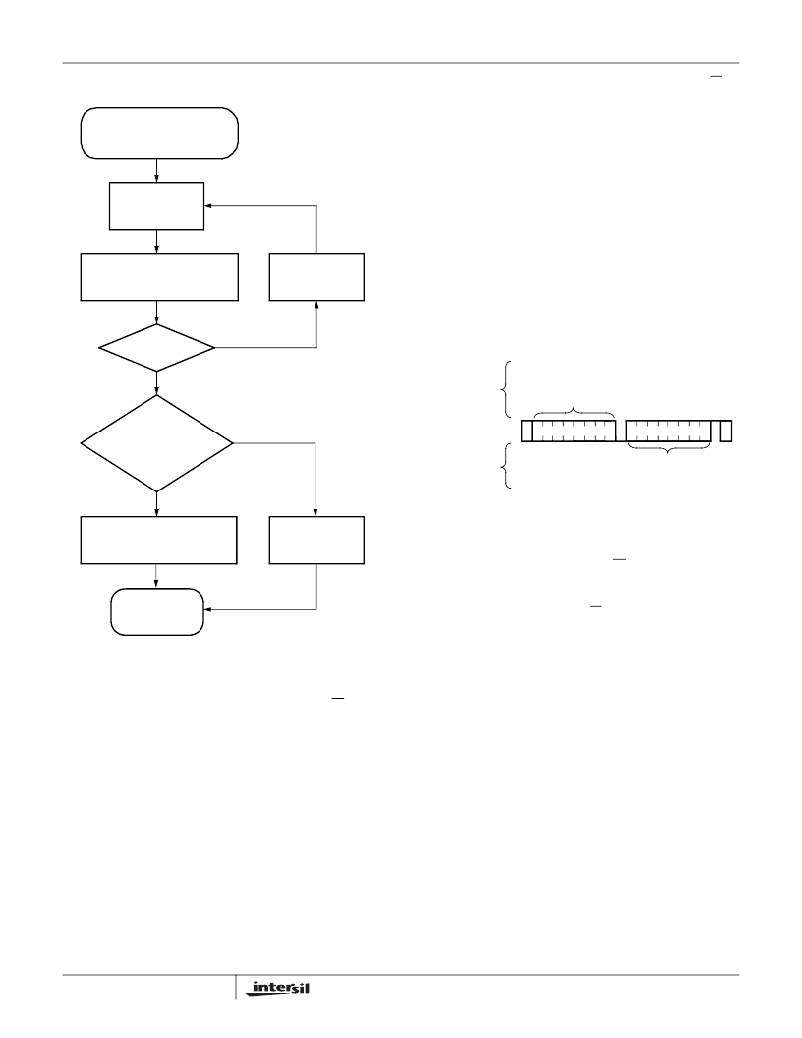

�Upon� receipt� of� the� Slave� Address� Byte� with� the� R/W� bit�

�set� to� one,� the� device� issues� an� acknowledge� and� then�

�transmits� the� eight� bits� of� the� Data� Byte.� The� master� ter-�

�minates� the� read� operation� when� it� does� not� respond�

�with� an� acknowledge� during� the� ninth� clock� and� then�

�issues� a� stop� condition.� Refer� to� Figure� 14� for� the�

�address,� acknowledge,� and� data� transfer� sequence.�

�It� should� be� noted� that� the� ninth� clock� cycle� of� the� read�

�operation� is� not� a� “don’t� care.”� To� terminate� a� read�

�operation,� the� master� must� either� issue� a� stop� condi-�

�tion� during� the� ninth� cycle� or� hold� SDA� HIGH� during�

�Issue� Slave�

�Address� Byte�

�(Read� or� Write)�

�ACK�

�Returned?�

�NO�

�Issue� Stop�

�the� ninth� clock� cycle� and� then� issue� a� stop� condition.�

�Note:� After� a� power-up� sequence,� the� first� read� cannot�

�be� a� current� address� read.�

�Figure� 14.� Current� Address� Read� Sequence�

�YES�

�High�

�Signals� from�

�the� Master�

�S�

�T�

�A�

�R�

�T�

�Slave�

�Address�

�S�

�T�

�O�

�P�

�Voltage�

�Cycle� Complete.�

�Continue�

�Sequence?�

�NO�

�SDA� Bus�

�Signals� from�

�the� Slave�

�S� 1� 0� 1� 0� 0� S� 1� S� 0� 1�

�A�

�C�

�K�

�Data�

�P�

�YES�

�Random� Read�

�Continue� Normal�

�Read� or� Write�

�Command� Sequence?�

�PROCEED�

�Issue� Stop�

�Random� read� operation� allows� the� master� to� access�

�any� memory� location� in� the� array.� Prior� to� issuing� the�

�Slave� Address� Byte� with� the� R/W� bit� set� to� one,� the�

�master� must� first� perform� a� “Dummy”� write� operation.�

�The� master� issues� the� start� condition� and� the� Slave�

�Address� Byte� with� the� R/W� bit� low,� receives� an�

�acknowledge,� then� issues� the� Word� Address� Byte� 1,�

�receives� another� acknowledge,� then� issues� the� Word�

�READ� OPERATIONS�

�Read� operations� are� initiated� in� the� same� manner� as�

�write� operations� with� the� exception� that� the� R/W� bit� of�

�the� Slave� Address� Byte� is� set� to� one.� There� are� three�

�basic� read� operations:� Current� Address� Reads,� Ran-�

�dom� Reads,� and� Sequential� Reads.� Refer� to� bus� tim-�

�ing� on� page� 21.�

�Current� Address� Read�

�Internally,� the� device� contains� an� address� counter� that�

�maintains� the� address� of� the� last� word� read� or� written�

�incremented� by� one.� After� a� read� operation� from� the�

�last� address� in� the� array,� the� counter� will� “roll� over”� to�

�the� first� address� in� the� array.� After� a� write� operation� to�

�the� last� address� in� a� given� page,� the� counter� will� “roll�

�over”� to� the� first� address� on� the� same� page.�

�16�

�Address� Byte� 0.� After� the� device� acknowledges� receipt�

�of� the� Word� Address� Byte� 0,� the� master� issues�

�another� start� condition� and� the� Slave� Address� Byte� with�

�the� R/W� bit� set� to� one.� This� is� followed� by� an� acknowl-�

�edge� and� then� eight� bits� of� data� from� the� device.� The�

�master� terminates� the� read� operation� by� not� respond-�

�ing� with� an� acknowledge� and� then� issuing� a� stop� con-�

�dition.� Refer� to� Figure� 9� for� the� address,� acknowledge,�

�and� data� transfer� sequence.�

�The� device� will� perform� a� similar� operation� called� “Set�

�Current� Address”� if� a� stop� is� issued� instead� of� the� sec-�

�ond� start� shown� in� Figure� 15.� The� device� will� go� into�

�standby� mode� after� the� stop� and� all� bus� activity� will� be�

�ignored� until� a� start� is� detected.� The� effect� of� this� oper-�

�ation� is� that� the� new� address� is� loaded� into� the�

�address� counter,� but� no� data� is� output� by� the� device.�

�The� next� Current� Address� Read� operation� will� read�

�from� the� newly� loaded� address.�

�FN8250.0�

�July� 29,� 2005�

�相关PDF资料 |

PDF描述 |

|---|---|

| X4645V8I-4.5A | IC SUPERVISOR CPU 64K EE 8-TSSOP |

| X4C105V20I | IC SUPERVISOR NOVRAM/EE 20-TSSOP |

| X5001V8I-4.5A | IC SUPERVISOR CPU 8-TSSOP |

| X5045V14I-4.5A | IC SUPERVISOR CPU 4K EE 14-TSSOP |

| X5083V8I-4.5A | IC SUPERVISOR CPU 8K EE 8-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X45BS4H47 | 制造商:n/a 功能描述:Power SCR |

| X45C613 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| X45C661 | 制造商:Harris Corporation 功能描述: |

| X45E333 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| X45E333E | 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。