参数资料

| 型号: | X45620V20I-2.7 |

| 厂商: | Intersil |

| 文件页数: | 18/20页 |

| 文件大小: | 0K |

| 描述: | IC VOLT MON DUAL SW EEPR 20TSSOP |

| 标准包装: | 75 |

| 类型: | 多压监控器 |

| 监视电压数目: | 2 |

| 输出: | 开路漏极或开路集电极 |

| 复位: | 低有效 |

| 复位超时: | 最小为 75 ms |

| 电压 - 阀值: | 1.75V,2.62V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

�� �

�

�

�X45620�

�WEL:� Write� Enable� Latch� (Volatile)�

�The� WEL� bit� controls� the� access� to� the� memory� and� to�

�the� Register� during� a� write� operation.� This� bit� is� a� volatile�

�latch� that� powers� up� in� the� LOW� (disabled)� state.� While�

�the� WEL� bit� is� LOW,� writes� to� any� address,� including� any�

�control� registers� will� be� ignored� (no� acknowledge� will� be�

�issued� after� the� Data� Byte).� The� WEL� bit� is� set� by� writing�

�a� “1”� to� the� WEL� bit� and� zeros� to� the� other� bits� of� the� con-�

�trol� register.� Once� set,� WEL� remains� set� until� either� it� is�

�reset� to� 0� (by� writing� a� “0”� to� the� WEL� bit� and� zeros� to� the�

�other� bits� of� the� control� register)� or� until� the� part� powers�

�up� again.� Writes� to� WEL� bit� do� not� cause� a� high� voltage�

�write� cycle,� so� the� device� is� ready� for� the� next� operation�

�immediately� after� the� stop� condition.�

�Write� Protect� Enable� Bit—WPEN� (Nonvolatile)�

�The� Write� Protect� (WP)� pin� and� the� Write� Protect� Enable�

�(WPEN)� bit� in� the� Control� Register� control� the� Program-�

�mable� Hardware� Write� Protect� feature.� Hardware� Write�

�Protection� is� enabled� when� the� WP� pin� is� connected� to�

�V� CC� and� the� WPEN� bit� is� HIGH,� and� disabled� when� WP�

�pin� is� connected� to� ground.� When� the� chip� is� in� ROM�

�mode,� nonvolatile� writes� are� disabled� to� all� non-volatile�

�bits� in� the� CR,� including� the� Block� Protect� bits� and� the�

�WPEN� bit� itself,� as� well� as� to� the� block� protected� sections�

�in� the� memory� array.� Only� the� sections� of� the� memory�

�array� that� are� not� block� protected� can� be� written.� Note�

�that� since� the� WPEN� bit� is� write� protected,� it� cannot� be�

�changed� back� to� a� LOW� state;� so� write� protection� is�

�enabled� as� long� as� the� WP� pin� is� held� connected� to� V� CC� .�

�BP1,� BP0:� Block� Protect� Bits� (Nonvolatile)�

�The� Block� Protect� Bits,� BP1� and� BP0,� determine� which�

�blocks� of� the� array� are� write� protected.� A� write� to� a� pro-�

�tected� block� of� memory� is� ignored.� The� block� protect� bits�

�will� prevent� write� operations� to� one� of� four� segments� of�

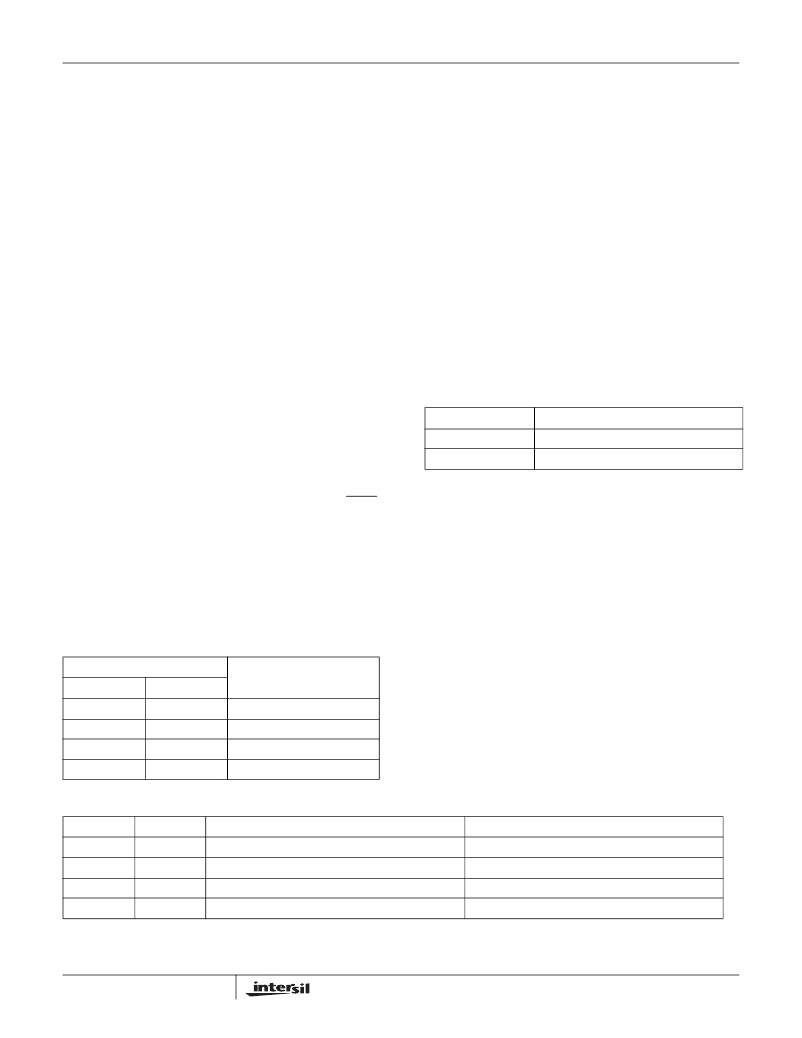

�PUP:� Power-on� Reset� (Nonvolatile)�

�The� Power-on� reset� time� (t� PURST� )� bit,� PUP,� sets� the�

�initial� power-on� reset� time.� There� are� two� standard�

�settings.�

�the� array.� The� partitions� are� described� in� Table� 2.�

�WD1,� WD0:� Watchdog� Timer� Bits� (Nonvolatile)�

�The� Watchdog� Timer� circuit� monitors� the� micro-�

�processor� activity� by� monitoring� the� SCL� and� SDA� pins.�

�PUP�

�0�

�1�

�Time�

�150� ms� (factory� settings)�

�800� ms�

�In� normal� operation,� the� microprocessor� must�

�periodically� restart� the� Watchdog� Timer� to� prevent� WDO�

�from� going� active.� The� watchdog� timer� is� restarted� on� the�

�first� HIGH� to� LOW� transition� on� SCL� after� a� start�

�command.� The� state� of� two� nonvolatile� control� bits� in� the�

�Status� Register� determines� the� watchdog� timer� period.�

�The� microprocessor� can� change� these� watchdog� bits� by�

�writing� to� the� status� register.�

�The� Watchdog� Timer� oscillator� stops� when� in� battery�

�backup� mode.� It� re-starts� when� V� CC� returns.�

�Note� 1.� Watchdog� timer� is� shipped� disabled.�

�2.� The� t� PURST� time� is� set� to� 150ms� at� the� factory.�

�Any� changes� to� the� Control� Register� take� effect,�

�following� either� the� next� command� (read� or� write)� or�

�cycling� the� power� to� the� device.�

�The� recommended� procedure� for� changing� the�

�Watchdog� Timer� settings� is� to� do� a� WREN,� followed�

�by� a� write� status� register� command.� Then� execute� a�

�software� loop� to� read� the� status� register� until� an� ACK�

�is� returned� (ACK� polling)� complete� the� read� operation.�

�Status� Register� Bit�

�WD1� WD0�

�0� 0�

�Watchdog� Time� Out�

�(Typical)�

�800� milliseconds�

�A� valid� alternative� is� to� do� a� WREN,� followed� by� a�

�write� status� register� command.� Then� wait� 10ms� and�

�do� a� read� status� command.�

�0�

�1�

�1�

�1�

�0�

�1�

�400� milliseconds�

�150� milliseconds�

�Disabled� (factory� setting)�

�Table� 2.� Block� Protect� Bits�

�BP1�

�0�

�0�

�1�

�1�

�BP0�

�0�

�1�

�0�

�1�

�18�

�Protected� Addresses�

�None�

�6000h� -� 7FFFh� (8K� bytes)�

�4000h� -� 7FFFh� (16K� bytes)�

�0000h� -� 7FFFh� (32K� bytes)�

�Array� Lock�

�None� (factory� setting)�

�Upper� 1/4� (Q4)�

�Upper� 1/2� (Q3,� Q4)�

�Full� Array� (All)�

�FN8250.0�

�July� 29,� 2005�

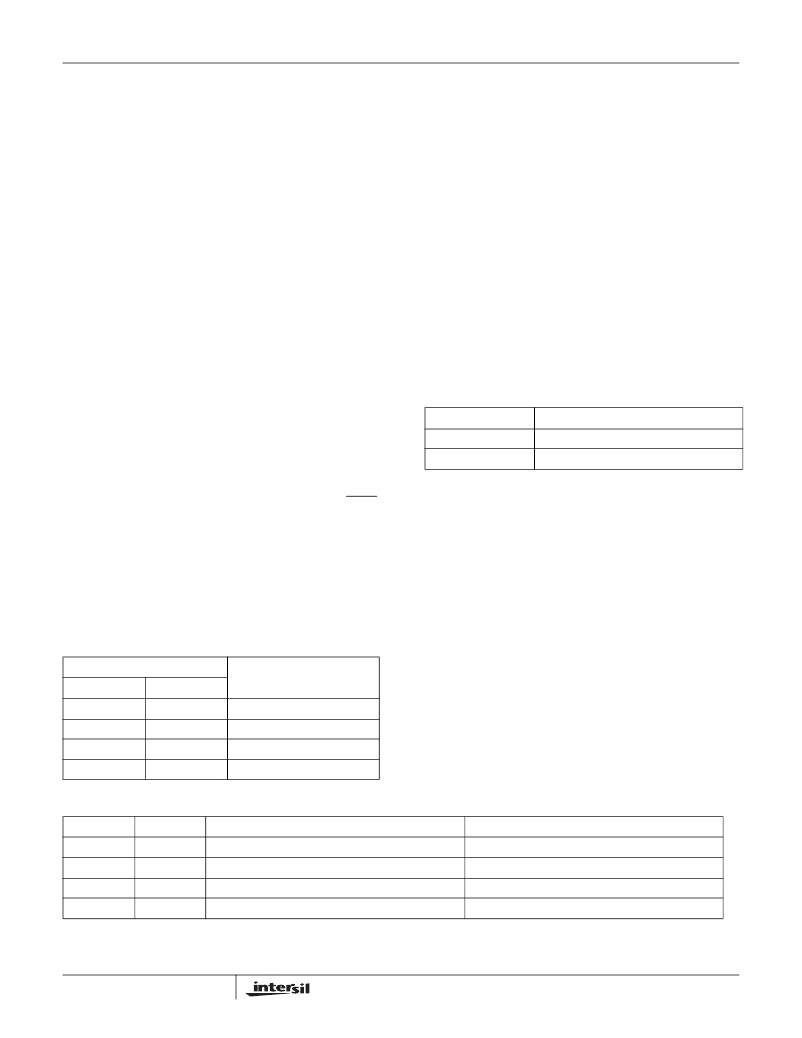

�相关PDF资料 |

PDF描述 |

|---|---|

| X4645V8I-4.5A | IC SUPERVISOR CPU 64K EE 8-TSSOP |

| X4C105V20I | IC SUPERVISOR NOVRAM/EE 20-TSSOP |

| X5001V8I-4.5A | IC SUPERVISOR CPU 8-TSSOP |

| X5045V14I-4.5A | IC SUPERVISOR CPU 4K EE 14-TSSOP |

| X5083V8I-4.5A | IC SUPERVISOR CPU 8K EE 8-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X45BS4H47 | 制造商:n/a 功能描述:Power SCR |

| X45C613 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| X45C661 | 制造商:Harris Corporation 功能描述: |

| X45E333 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述: |

| X45E333E | 制造商:Harris Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。