参数资料

| 型号: | X96012V14IZT1 |

| 厂商: | Intersil |

| 文件页数: | 4/23页 |

| 文件大小: | 0K |

| 描述: | IC BIAS CTRLR UNIV SNSR 14-TSSOP |

| 标准包装: | 2,500 |

| 类型: | 传感器调节器 |

| 输入类型: | 电压 |

| 输出类型: | 电压 |

| 接口: | 2 线 |

| 电流 - 电源: | 15mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 14-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 14-TSSOP |

| 包装: | 带卷 (TR) |

12

FN8216.3

February 20, 2008

Control Register 4

This register is accessed by performing a Read or Write

operation to address 84h of memory. This byte’s volatility is

determined by bit NV1234 in Control register 0.

D2DA7 - D2DA0: D/A 2 DIRECT ACCESS BITS

When bit D2DAS (bit 7 in Control register 5) is set to “1”, the

input to the D/A converter 1 is the content of bits

D2DA-D2DA0, and it is not a row of LUT2. When bit D2DAS

is set to “0” (default) these eight bits are ignored by the

X96012. See Figure 9.

Control Register 5

This register is accessed by performing a Read or Write

operation to address 85h of memory.

I1FSO1 - I1FSO0: CURRENT GENERATOR 1 FULL

SCALE OUTPUT SET BITS (NON-VOLATILE)

These two bits are used to set the full scale output current at

the Current Generator 1 pin, I1. If both bits are set to “0”

(default), an external resistor connected between pin R1 and

VSS, determines the full scale output current available at pin

I1. The other three options are indicated in Table 2. The

direction of this current is set by bit I1DS in Control register

0. See Figure 8.

I2FSO1 - I2FSO0: CURRENT GENERATOR 2 FULL

SCALE OUTPUT CURRENT SET BITS (NON-VOLATILE)

These two bits are used to set the full scale output current at

the Current Generator 2 pin, I2. If both bits are set to “0”

(default), an external resistor connected between pin R2 and

Vss, determines the full scale output current available at pin

I2. The other three options are indicated Table 3. The direction

of this current is set by bit I2DS in Control Register 0.

L1DAS: LUT1 DIRECT ACCESS SELECT BIT

(NON-VOLATILE)

When bit L1DAS is set to “0” (default), LUT1 is addressed by

the output of the on-chip A/D converter. When bit L1DAS is

set to “1”, LUT1 is addressed by bits L1DA5 - L1DA0.

D1DAS: D/A 1 DIRECT ACCESS SELECT BIT

(NON-VOLATILE)

When bit D1DAS is set to “0” (default), the input to the D/A

converter 1 is a row of LUT1. When bit D1DAS is set to “1”, that

input is the content of the Control register 3.

L2DAS: LUT2 DIRECT ACCESS SELECT BIT

(NON-VOLATILE)

When bit L2DAS is set to “0” (default), LUT2 is addressed by

the output of the on-chip A/D converter. When bit L2DAS is

set to “1”, LUT2 is addressed by bits L2DA5 - L2DA0.

D2DAS: D/A 2 DIRECT ACCESS SELECT BIT

(NONVOLATILE)

When bit D2DAS is set to “0” (default), the input to the D/A

converter 2 is a row of LUT2. When bit D2DAS is set to “1”, that

input is the content of the Control register 4.

Control Register 6

This register is accessed by performing a Read or Write

operation to address 86h of memory.

WEL: WRITE ENABLE LATCH (VOLATILE)

The WEL bit controls the Write Enable status of the entire

X96012 device. This bit must be set to “1” before any other

Write operation (volatile or nonvolatile). Otherwise, any

proceeding Write operation to memory is aborted and no ACK

is issued after a Data Byte.

The WEL bit is a volatile latch that powers up in the “0” state

(disabled). The WEL bit is enabled by writing 100000002 to

Control register 6. Once enabled, the WEL bit remains set to “1”

until the X96012 is powered down, and then up again, or until it

is reset to “0” by writing 000000002 to Control register 6.

A Write operation that modifies the value of the WEL bit will not

cause a change in other bits of Control register 6.

Status Register - ADC Output

This register is accessed by performing a Read operation to

address 87h of memory.

AD7 - AD0: A/D CONVERTER OUTPUT BITS (READ

ONLY)

These eight bits are the binary output of the on-chip A/D

converter. The output is 000000002 for minimum input and

111111112 for full scale input. The six MSBs select a row of

the LUTs.

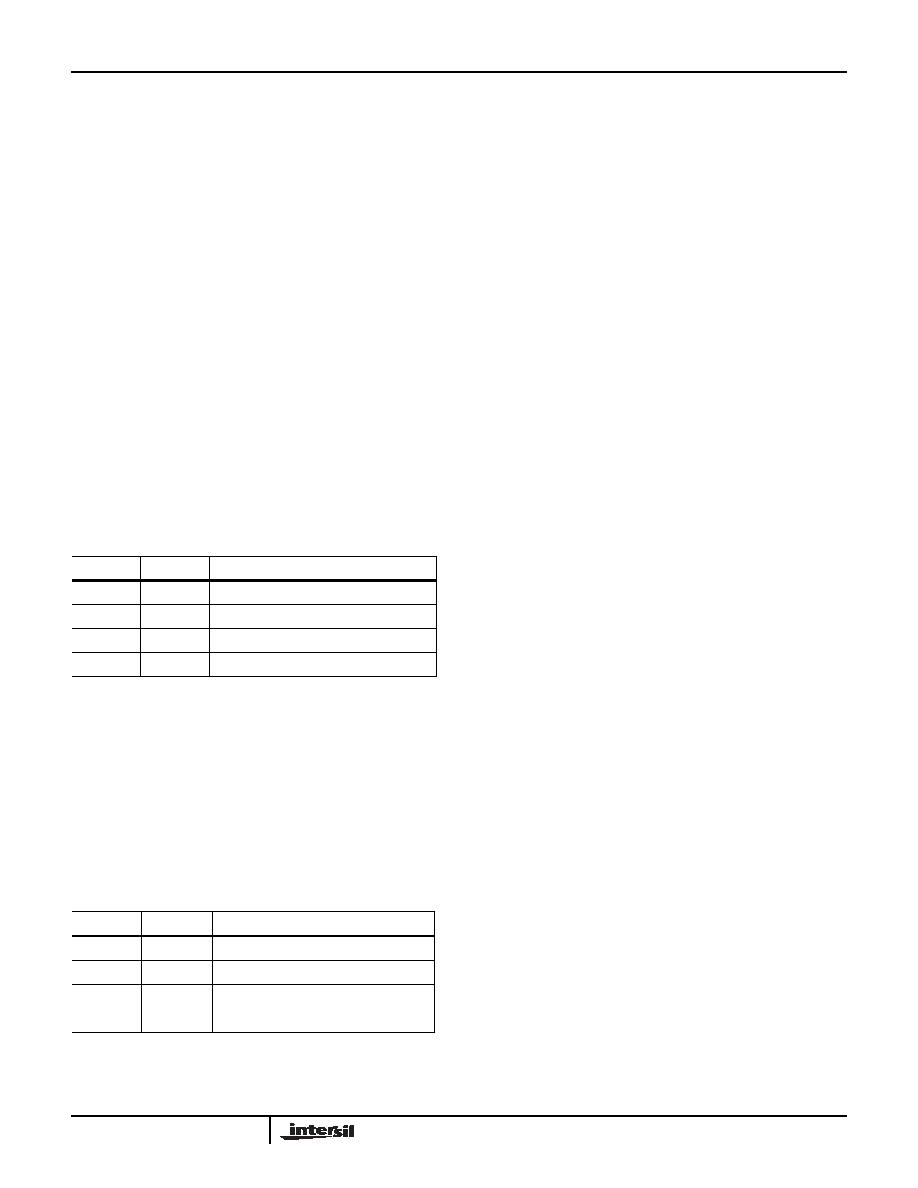

TABLE 2.

I1FSO1

I1FSO0

I1 FULL SCALE OUTPUT CURRENT

0

Set externally via pin R1 (Default)

01

±0.4mA*

1

0

±0.85mA*

11

±1.3mA*

NOTE: *No external resistor should be connected in these cases

between R1 and VSS.

TABLE 3.

I2FSO1

I2FSO2

I2 FULL SCALE OUTPUT CURRENT

0

Set externally via pin R2 (Default)

0

1

±0.4mA*

10

±0.85mA*

1

±1.3mA*

NOTE: *No external resistor should be connected in these cases

between R2 and VSS.

X96012

相关PDF资料 |

PDF描述 |

|---|---|

| X9C303V8T2 | IC XDCP 100-TAP 32K EE 8-TSSOP |

| X9C503ST2 | IC XDCP 100-TAP 50K EE 8-SOIC |

| XA2C128-8CPG132Q | IC CPLD 128MC 100 I/O 132CSBGA |

| XA2C32A-7VQG44Q | IC CPLD 32MCELL 33 I/O 44-VQFP |

| XA2C384-11TQG144Q | IC CPLD 384MCELL 118 I/O 144TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| X9601XEVAL | 制造商:Intersil Corporation 功能描述:X9601 EVALUATION BOARD - Bulk |

| X9650M | 制造商:EPCOS 制造商全称:EPCOS 功能描述:Bandpass Filter |

| X-97-488 | 制造商:Brady Corporation 功能描述:Labels External Width:0.9" 制造商:Brady Corporation 功能描述:LABEL IDENTIFICATION 22.86X22.86 BLK/WHT; Background Color:White; Color:Black on White; External Width:0.9"; For Use With:IDXPERT Hand-Held Labeler; Label Material:Polyester; Label Size:22.86 x 22.86mm; Label Type:Identification ;RoHS Compliant: Yes |

| X97494 | 制造商:Mersen 功能描述:FUSE BS88-4 25A |

| X98014 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:140MHz Triple Video Digitizer with Digital PLL |

发布紧急采购,3分钟左右您将得到回复。