参数资料

| 型号: | XC2S100-5FGG256C |

| 厂商: | Xilinx Inc |

| 文件页数: | 67/99页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 100K 256-FBGA |

| 标准包装: | 90 |

| 系列: | Spartan®-II |

| LAB/CLB数: | 600 |

| 逻辑元件/单元数: | 2700 |

| RAM 位总计: | 40960 |

| 输入/输出数: | 176 |

| 门数: | 100000 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 256-BGA |

| 供应商设备封装: | 256-FBGA(17x17) |

| 其它名称: | 122-1302 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页当前第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

7

2000-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other

trademarks are the property of their respective owners.

Architectural Description

Spartan-II FPGA Array

The Spartan-II field-programmable gate array, shown in

Figure 2, is composed of five major configurable elements:

IOBs provide the interface between the package pins

and the internal logic

CLBs provide the functional elements for constructing

most logic

Dedicated block RAM memories of 4096 bits each

Clock DLLs for clock-distribution delay compensation

and clock domain control

Versatile multi-level interconnect structure

As can be seen in Figure 2, the CLBs form the central logic

structure with easy access to all support and routing

structures. The IOBs are located around all the logic and

memory elements for easy and quick routing of signals on

and off the chip.

Values stored in static memory cells control all the

configurable logic elements and interconnect resources.

These values load into the memory cells on power-up, and

can reload if necessary to change the function of the device.

Each of these elements will be discussed in detail in the

following sections.

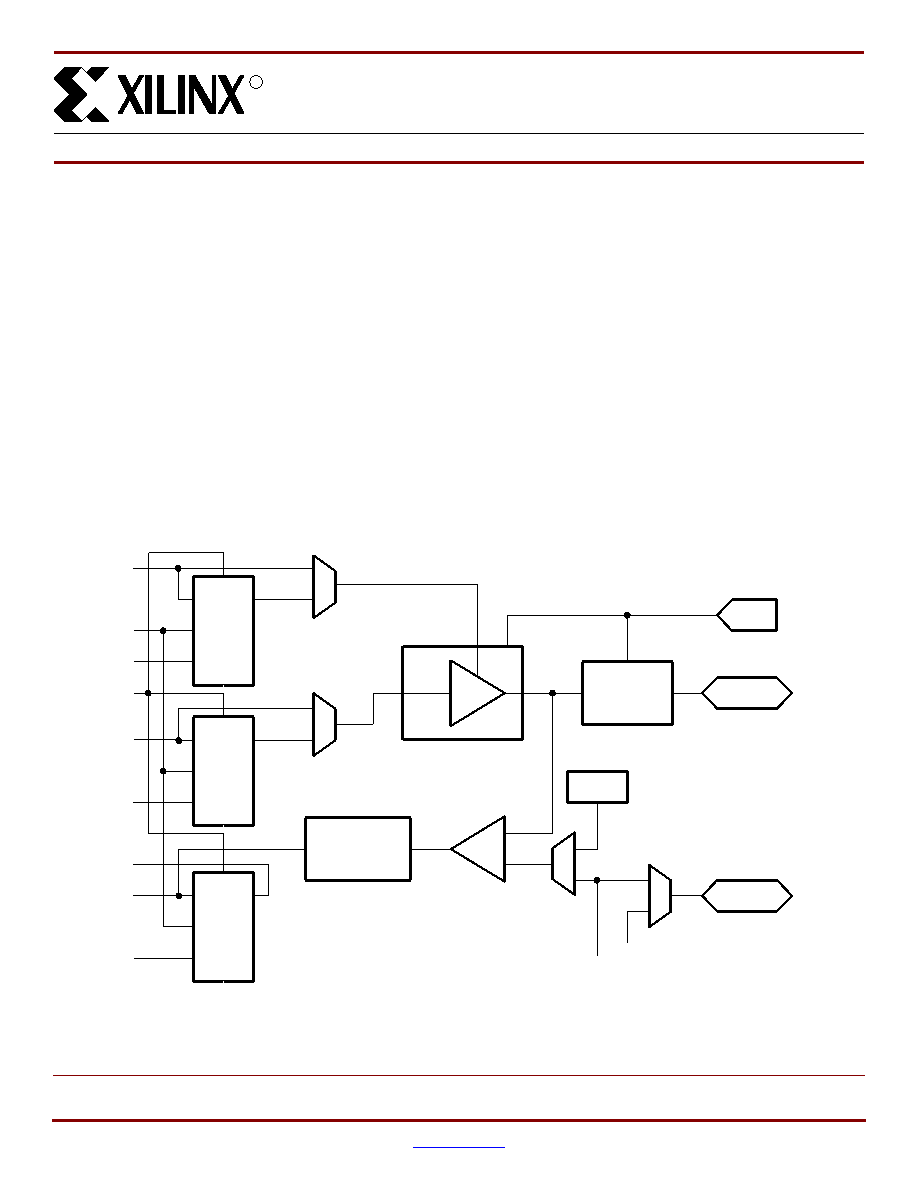

Input/Output Block

The Spartan-II FPGA IOB, as seen in Figure 2, features

inputs and outputs that support a wide variety of I/O

signaling standards. These high-speed inputs and outputs

are capable of supporting various state of the art memory

and bus interfaces. Table 3 lists several of the standards

which are supported along with the required reference,

output and termination voltages needed to meet the

standard.

50

Spartan-II FPGA Family:

Functional Description

DS001-2 (v2.8) June 13, 2008

Product Specification

R

Figure 2: Spartan-II FPGA Input/Output Block (IOB)

Package Pin

Package

Pin

Package Pin

D

CK

EC

SR

Q

D

CK

EC

SR

Q

D

CK

EC

SR

Q

Programmable

Bias &

ESD Network

VCCO

I/O

I/O, VREF

Internal

Reference

To Next I/O

To Other

External VREF Inputs

of Bank

Programmable

Input Buffer

Programmable

Output Buffer

Programmable

Delay

VCC

OE

SR

O

OCE

I

ICE

IQ

CLK

TCE

T

DS001_02_090600

TFF

OFF

IFF

相关PDF资料 |

PDF描述 |

|---|---|

| AMM24DTBT | CONN EDGECARD 48POS R/A .156 SLD |

| AMM24DTAT | CONN EDGECARD 48POS R/A .156 SLD |

| AMC31DRXS-S734 | CONN EDGECARD 62POS DIP .100 SLD |

| ABC60DRXN-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| ABC60DRXH-S734 | CONN EDGECARD 120PS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S100-5FGG256I | 功能描述:IC SPARTAN-II FPGA 100K 256-FBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S100-5FGG456C | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S100-5FGG456I | 制造商:XILINX 制造商全称:XILINX 功能描述:Spartan-II FPGA Family |

| XC2S100-5PQ208C | 功能描述:IC FPGA 2.5V 600 CLB'S 208-PQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S1005PQ208I | 制造商:Xilinx 功能描述: |

发布紧急采购,3分钟左右您将得到回复。