参数资料

| 型号: | XC6VCX195T-2FFG784I |

| 厂商: | Xilinx Inc |

| 文件页数: | 26/52页 |

| 文件大小: | 0K |

| 描述: | IC FPGA VIRTEX 6 199K 784FFGBGA |

| 产品培训模块: | Virtex-6 FPGA Overview |

| 产品变化通告: | Virtex-6 FIFO Input Logic Reset 18/Apr/2011 |

| 标准包装: | 1 |

| 系列: | Virtex® 6 CXT |

| LAB/CLB数: | 15600 |

| 逻辑元件/单元数: | 199680 |

| RAM 位总计: | 12681216 |

| 输入/输出数: | 400 |

| 电源电压: | 0.95 V ~ 1.05 V |

| 安装类型: | 表面贴装 |

| 工作温度: | -40°C ~ 100°C |

| 封装/外壳: | 784-BBGA,FCBGA |

| 供应商设备封装: | 784-FCBGA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页

Virtex-6 CXT Family Data Sheet

DS153 (v1.6) February 11, 2011

Product Specification

32

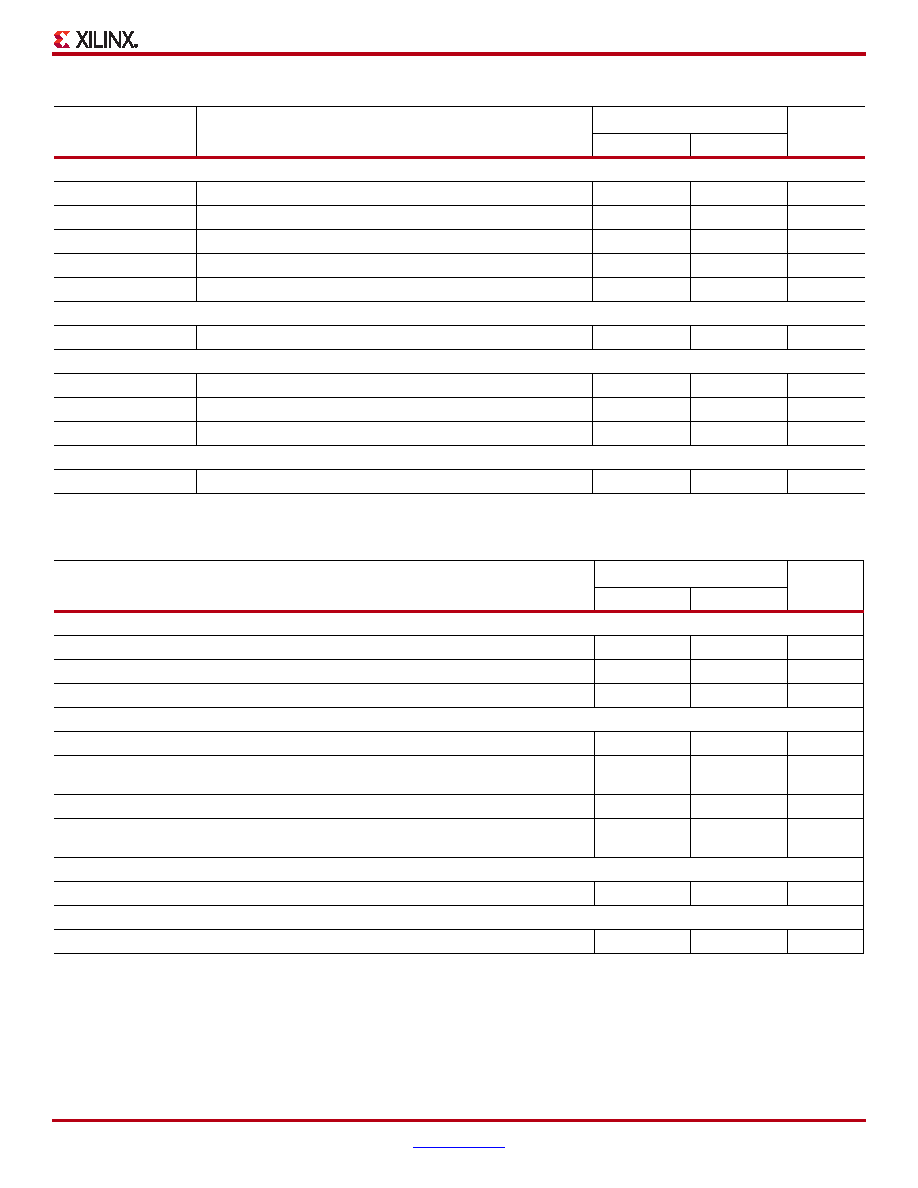

Input Serializer/Deserializer Switching Characteristics

Table 43: OLOGIC Switching Characteristics

Symbol

Description

Speed Grade

Units

-2

-1

Setup/Hold

TODCK/TOCKD

D1/D2 pins Setup/Hold with respect to CLK

0.54/–0.11

ns

TOOCECK/TOCKOCE

OCE pin Setup/Hold with respect to CLK

0.22/–0.05

ns

TOSRCK/TOCKSR

SR pin Setup/Hold with respect to CLK

0.71/–0.29

ns

TOTCK/TOCKT

T1/T2 pins Setup/Hold with respect to CLK

0.56/–0.10

ns

TOTCECK/TOCKTCE

TCE pin Setup/Hold with respect to CLK

0.21/–0.05

ns

Combinatorial

TDOQ

D1 to OQ out or T1 to TQ out

1.01

ns

Sequential Delays

TOCKQ

CLK to OQ/TQ out

0.71

ns

TRQ

SR pin to OQ/TQ out

1.05

ns

TGSRQ

Global Set/Reset to Q outputs

10.51

ns

Set/Reset

TRPW

Minimum Pulse Width, SR inputs

1.20

ns, Min

Table 44: ISERDES Switching Characteristics

Symbol

Description

Speed Grade

Units

-2

-1

Setup/Hold for Control Lines

TISCCK_BITSLIP/ TISCKC_BITSLIP

BITSLIP pin Setup/Hold with respect to CLKDIV

0.09/0.17

ns

CE pin Setup/Hold with respect to CLK (for CE1)

0.27/0.04

ns

CE pin Setup/Hold with respect to CLKDIV (for CE2)

–0.06/0.31

ns

Setup/Hold for Data Lines

TISDCK_D /TISCKD_D

D pin Setup/Hold with respect to CLK

0.09/0.11

ns

TISDCK_DDLY /TISCKD_DDLY

DDLY pin Setup/Hold with respect to CLK (using

IODELAY)(1)

0.14/0.07

ns

TISDCK_D_DDR /TISCKD_D_DDR

D pin Setup/Hold with respect to CLK at DDR mode

0.09/0.11

ns

TISDCK_DDLY_DDR

TISCKD_DDLY_DDR

D pin Setup/Hold with respect to CLK at DDR mode

(using IODELAY)(1)

0.14/0.07

ns

Sequential Delays

TISCKO_Q

CLKDIV to out at Q pin

0.75

ns

Propagation Delays

TISDO_DO

D input to DO output pin

0.25

ns

Notes:

1.

Recorded at 0 tap value.

2.

TISCCK_CE2 and TISCKC_CE2 are reported as TISCCK_CE/TISCKC_CE in a TRACE report.

相关PDF资料 |

PDF描述 |

|---|---|

| ABB106DHFN-S578 | EDGECARD 212POS .050 SMD W/POSTS |

| XC5VLX110-1FFG1760C | IC FPGA VIRTEX-5 110K 1760FBGA |

| ACB106DHFD-S578 | EDGECARD 212POS .050 SMD W/POSTS |

| ABB106DHFD-S578 | EDGECARD 212POS .050 SMD W/POSTS |

| XC5VLX110-1FFG1153C | IC FPGA VIRTEX-5 110K 1153FBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC6VCX240T | 制造商:XILINX 制造商全称:XILINX 功能描述:Virtex-6 CXT Family Data Sheet |

| XC6VCX240T-1FF1156C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 241152 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA 600 I/O 1156FCBGA |

| XC6VCX240T-1FF1156I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 241152 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 240K 1156BGA 制造商:Xilinx 功能描述:IC FPGA 600 I/O 1156FCBGA |

| XC6VCX240T-1FF784C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 241152 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 240K 784BGA |

| XC6VCX240T-1FF784I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 241152 CELLS 40NM (CMOS) TECHNOLOG - Trays 制造商:Xilinx 功能描述:IC FPGA 400 I/O 784FCBGA |

发布紧急采购,3分钟左右您将得到回复。