- 您现在的位置:买卖IC网 > PDF目录19907 > XCF01SVOG20C (Xilinx Inc)IC PROM SRL FOR 1M GATE 20-TSSOP PDF资料下载

参数资料

| 型号: | XCF01SVOG20C |

| 厂商: | Xilinx Inc |

| 文件页数: | 2/35页 |

| 文件大小: | 0K |

| 描述: | IC PROM SRL FOR 1M GATE 20-TSSOP |

| 标准包装: | 74 |

| 可编程类型: | 系统内可编程 |

| 存储容量: | 1Mb |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 601 (CN2011-ZH PDF) |

| 其它名称: | 122-1286-5 |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

Platform Flash In-System Programmable Configuration PROMs

DS123 (v2.18) May 19, 2010

Product Specification

10

R

Initiating FPGA Configuration

The options for initiating FPGA configuration via the

Platform Flash PROM include:

Automatic configuration on power up

Applying an external pulse to the FPGA PROGRAM_B

pin

Applying the JTAG CONFIG instruction to the PROM

Following the FPGA’s power-on sequence or the assertion

of the PROGRAM_B pin, the FPGA’s configuration memory

is cleared, the configuration mode is selected, and the

FPGA is ready to accept a new configuration bitstream. The

FPGA’s PROGRAM_B pin can be controlled by an external

source, or alternatively, the Platform Flash PROMs

incorporate a CF pin that can be tied to the FPGA’s

PROGRAM_B pin. Executing the CONFIG instruction

through JTAG pulses the CF output Low once for

300-500 ns, resetting the FPGA and initiating configuration.

The iMPACT software can issue the JTAG CONFIG

command to initiate FPGA configuration by setting the

“Load FPGA” option.

When using the XCFxxP Platform Flash PROM with design

revisioning enabled, the CF pin should always be connected

to the PROGRAM_B pin on the FPGA to ensure that the

current design revision selection is sampled when the

FPGA is reset. The XCFxxP PROM samples the current

design revision selection from the external REV_SEL pins

or the internal programmable Revision Select bits on the

rising edge of CF. When the JTAG CONFIG command is

executed, the XCFxxP samples the new design revision

selection before initiating the FPGA configuration

sequence. When using the XCFxxP Platform Flash PROM

without design revisioning, if the CF pin is not connected to

the FPGA PROGRAM_B pin, then the XCFxxP CF pin must

be tied High.

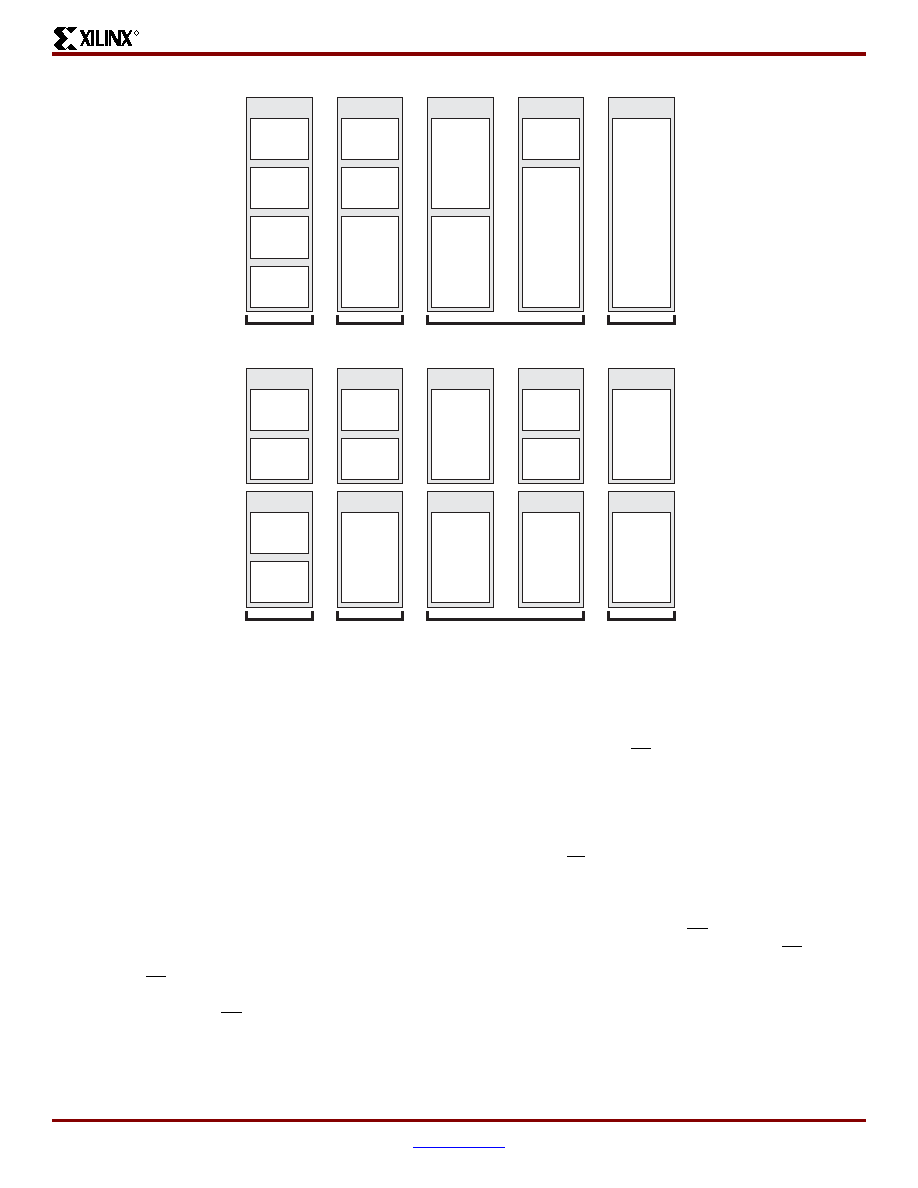

X-Ref Target - Figure 5

Figure 5: Design Revision Storage Examples

REV 0

(8 Mbits)

REV 1

(8 Mbits)

REV 2

(8 Mbits)

REV 3

(8 Mbits)

REV 0

(8 Mbits)

REV 1

(8 Mbits)

REV 2

(16 Mbits)

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 0

(8 Mbits)

REV 1

(24 Mbits)

REV 0

(32 Mbits)

4 Design Revisions

3 Design Revisions

2 Design Revisions

1 Design Revision

(a) Design Revision storage examples for a single XCF32P PROM

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 2

(16 Mbits)

REV 3

(16 Mbits)

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 2

(32 Mbits)

REV 0

(32 Mbits)

REV 1

(32 Mbits)

REV 0

(16 Mbits)

REV 1

(16 Mbits)

REV 0

(32 Mbits)

4 Design Revisions

3 Design Revisions

2 Design Revisions

1 Design Revision

(b) Design Revision storage examples spanning two XCF32P PROMs

PROM 0

REV 0

(32 Mbits)

REV 1

(32 Mbits)

PROM 1

ds123_20_102103

相关PDF资料 |

PDF描述 |

|---|---|

| EEM10DRYF | CONN EDGECARD 20POS DIP .156 SLD |

| V48C8H100BG | CONVERTER MOD DC/DC 8V 100W |

| EPC16UC88N | IC CONFIG DEVICE 16MBIT 88-UBGA |

| LTC4301IDD#TR | IC BUFFER BUS HOTSWAP 2WR 8DFN |

| AGM22DTBH | CONN EDGECARD 44POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCF01SVOG20C0100 | 制造商:Xilinx 功能描述:XLXXCF01SVOG20C0100 IC SYSTEM GATE |

| XCF01SVOG20C0936 | 制造商:Xilinx 功能描述:XLXXCF01SVOG20C0936 IC SYSTEM GATE |

| XCF01SVOG48 | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF01SX | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF02S | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

发布紧急采购,3分钟左右您将得到回复。