- 您现在的位置:买卖IC网 > PDF目录19907 > XCF01SVOG20C (Xilinx Inc)IC PROM SRL FOR 1M GATE 20-TSSOP PDF资料下载

参数资料

| 型号: | XCF01SVOG20C |

| 厂商: | Xilinx Inc |

| 文件页数: | 4/35页 |

| 文件大小: | 0K |

| 描述: | IC PROM SRL FOR 1M GATE 20-TSSOP |

| 标准包装: | 74 |

| 可编程类型: | 系统内可编程 |

| 存储容量: | 1Mb |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 20-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 20-TSSOP |

| 包装: | 管件 |

| 产品目录页面: | 601 (CN2011-ZH PDF) |

| 其它名称: | 122-1286-5 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

Platform Flash In-System Programmable Configuration PROMs

DS123 (v2.18) May 19, 2010

Product Specification

12

R

Standby Mode

The PROM enters a low-power standby mode whenever CE is

deasserted (High). In standby mode, the address counter is

reset, CEO is driven High, and the remaining outputs are

placed in a high-impedance state regardless of the state of the

OE/RESET input. For the device to remain in the low-power

standby mode, the JTAG pins TMS, TDI, and TDO must not be

pulled Low, and TCK must be stopped (High or Low).

When using the FPGA DONE signal to drive the PROM CE

pin High to reduce standby power after configuration, an

external pull-up resistor should be used. Typically a 330

Ω

pull-up resistor is used, but refer to the appropriate FPGA

data sheet for the recommended DONE pin pull-up value. If

the DONE circuit is connected to an LED to indicate FPGA

configuration is complete, and is also connected to the

PROM CE pin to enable low-power standby mode, then an

external buffer should be used to drive the LED circuit to

ensure valid transitions on the PROM’s CE pin. If low-power

standby mode is not required for the PROM, then the CE pin

should be connected to ground.

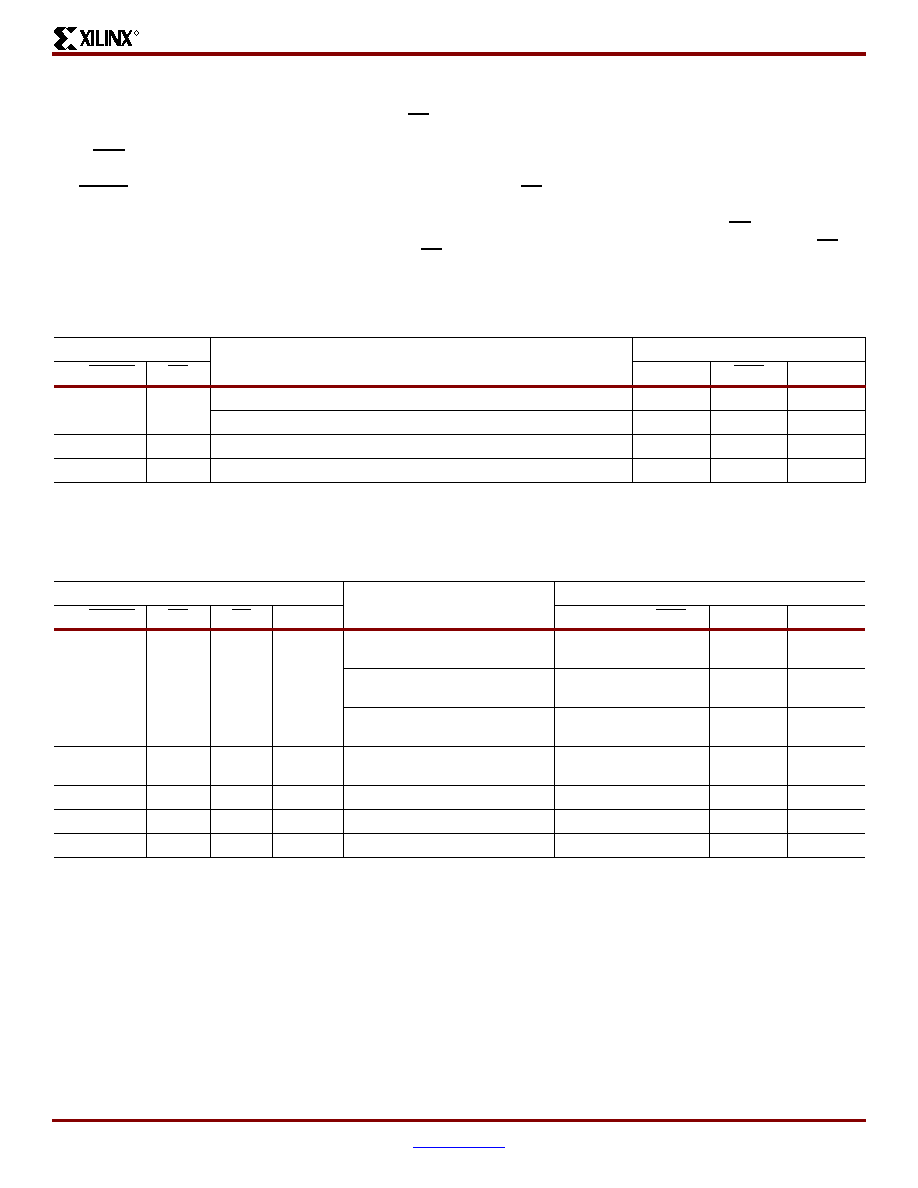

Table 10: Truth Table for XCFxxS PROM Control Inputs

Control Inputs

Internal Address

Outputs

OE/RESET

CE

DATA

CEO

ICC

High

Low

If address

< TC(2) : increment

Active

High

Active

If address

= TC(2) : don't change

High-Z

Low

Reduced

Low

Held reset

High-Z

High

Active

X(1)

High

Held reset

High-Z

High

Standby

Notes:

1.

X = don’t care.

2.

TC = Terminal Count = highest address value.

Table 11: Truth Table for XCFxxP PROM Control Inputs

Control Inputs

Internal Address

Outputs

OE/RESET

CE

CF

BUSY(5)

DATA

CEO

CLKOUT

ICC

High

Low

High

Low

If address

< TC(2) and

address

< EA(3) : increment

Active

High

Active

If address

< TC(2) and

address

= EA(3) : don't change

High-Z

High

High-Z

Reduced

Else

If address

= TC(2) : don't change

High-Z

Low

High-Z

Reduced

High

Low

High

Unchanged

Active and

Unchanged

High

Active

High

Low

↑

X(1)

Reset(4)

Active

High

Active

Low

X

Held reset(4)

High-Z

High

High-Z

Active

X

High

X

Held reset(4)

High-Z

High

High-Z

Standby

Notes:

1.

X = don’t care.

2.

TC = Terminal Count = highest address value.

3.

For the XCFxxP with Design Revisioning enabled, EA = end address (last address in the selected design revision).

4.

For the XCFxxP with Design Revisioning enabled, Reset = address reset to the beginning address of the selected bank. If Design

Revisioning is not enabled, then Reset = address reset to address 0.

5.

The BUSY input is only enabled when the XCFxxP is programmed for parallel data output and decompression is not enabled.

相关PDF资料 |

PDF描述 |

|---|---|

| EEM10DRYF | CONN EDGECARD 20POS DIP .156 SLD |

| V48C8H100BG | CONVERTER MOD DC/DC 8V 100W |

| EPC16UC88N | IC CONFIG DEVICE 16MBIT 88-UBGA |

| LTC4301IDD#TR | IC BUFFER BUS HOTSWAP 2WR 8DFN |

| AGM22DTBH | CONN EDGECARD 44POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XCF01SVOG20C0100 | 制造商:Xilinx 功能描述:XLXXCF01SVOG20C0100 IC SYSTEM GATE |

| XCF01SVOG20C0936 | 制造商:Xilinx 功能描述:XLXXCF01SVOG20C0936 IC SYSTEM GATE |

| XCF01SVOG48 | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF01SX | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMS |

| XCF02S | 制造商:XILINX 制造商全称:XILINX 功能描述:Platform Flash In-System Programmable Configuration PROMs |

发布紧急采购,3分钟左右您将得到回复。