参数资料

| 型号: | XIO2200AGGW |

| 厂商: | Texas Instruments |

| 文件页数: | 153/202页 |

| 文件大小: | 0K |

| 描述: | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| 产品培训模块: | PCI Express Basics |

| 标准包装: | 126 |

| 应用: | PCI Express 至 PCI 转换桥 |

| 接口: | PCI |

| 电源电压: | 1.35 V ~ 1.65 V,3 V ~ 3.6 V |

| 封装/外壳: | 176-LFBGA |

| 供应商设备封装: | 176-BGA MICROSTAR(15x15) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 882 (CN2011-ZH PDF) |

| 配用: | XIO2200AEVM-ND - XIO2200AEVM |

| 其它名称: | 296-19617 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页当前第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页

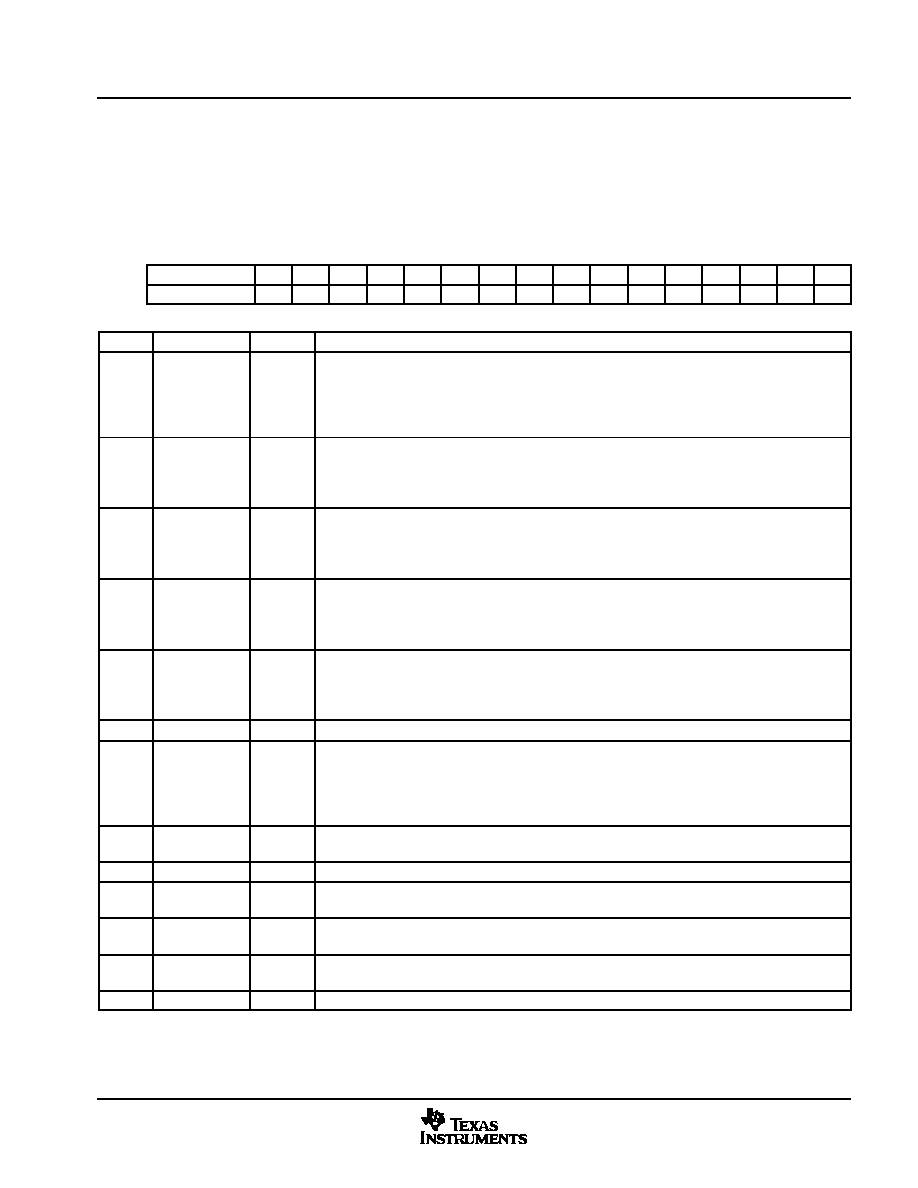

Classic PCI Configuration Space

41

March 5 2007 June 2011

SCPS154C

4.4

Status Register

The status register provides information about the PCI Express interface to the system. See Table 43 for a

complete description of the register contents.

PCI register offset:

06h

Register type:

Read-only, Read/Clear

Default value:

0010h

BIT NUMBER

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RESET STATE

0

1

0

Table 43. Status Register Description

BIT

FIELD NAME

ACCESS

DESCRIPTION

15

PAR_ERR

RCU

Detected parity error. This bit is set when the PCI Express interface receives a poisoned TLP. This

bit is set regardless of the state of bit 6 (PERR_ENB) in the command register (offset 04h, see

Section 4.3).

0 = No parity error detected

1 = Parity error detected

14

SYS_ERR

RCU

Signaled system error. This bit is set when the bridge sends an ERR_FATAL or ERR_NONFATAL

message and bit 8 (SERR_ENB) in the command register (offset 04h, see Section 4.3) is set.

0 = No error signaled

1 = ERR_FATAL or ERR_NONFATAL signaled

13

MABORT

RCU

Received master abort. This bit is set when the PCI Express interface of the bridge receives a

completion-with-unsupported-request status.

0 = Unsupported request not received on the PCI Express interface

1 = Unsupported request received on the PCI Express interface

12

TABORT_REC

RCU

Received target abort. This bit is set when the PCI Express interface of the bridge receives a

completion-with-completer-abort status.

0 = Completer abort not received on the PCI Express interface

1 = Completer abort received on the PCI Express interface

11

TABORT_SIG

RCU

Signaled target abort. This bit is set when the PCI Express interface completes a request with

completer abort status.

0 = Completer abort not signaled on the PCI Express interface

1 = Completer abort signaled on the PCI Express interface

10:9

PCI_SPEED

R

DEVSEL timing. These bits are read-only 00b, because they do not apply to PCI Express.

8

DATAPAR

RCU

Master data parity error. This bit is set if bit 6 (PERR_ENB) in the command register (offset 04h,

see Section 4.3) is set and the bridge receives a completion with data marked as poisoned on the

PCI Express interface or poisons a write request received on the PCI Express interface.

0 = No uncorrectable data error detected on the primary interface

1 = Uncorrectable data error detected on the primary interface

7

FBB_CAP

R

Fast back-to-back capable. This bit does not have a meaningful context for a PCI Express device

and is hardwired to 0b.

6

RSVD

R

Reserved. Returns 0b when read.

5

66MHZ

R

66-MHz capable. This bit does not have a meaningful context for a PCI Express device and is

hardwired to 0b.

4

CAPLIST

R

Capabilities list. This bit returns 1b when read, indicating that the bridge supports additional PCI

capabilities.

3

INT_STATUS

R

Interrupt status. This bit reflects the interrupt status of the function. This bit is read-only 0b since

the bridge does not generate any interrupts internally.

2:0

RSVD

R

Reserved. Returns 000b when read.

Not Recommended for New Designs

相关PDF资料 |

PDF描述 |

|---|---|

| XIO2200AZGW | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| XPC823ZT81B2T | IC MPU POWERQUICC 81MHZ 256-PBGA |

| XPC8240RZU250E | MCU HOST PROCESSOR 352-TBGA |

| XQ6SLX150T-3CSG484I | IC FPGA SPARTAN-6Q 484-CSBGA |

| XR16C2550IJ-F | IC UART FIFO 16B DUAL 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XIO2200AZGW | 功能描述:外围驱动器与原件 - PCI PCI Exp-PCI Bus Trans Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XIO2200AZGW | 制造商:Texas Instruments 功能描述:PCI Express to PCI Bus Converter IC |

| XIO2200AZHH | 功能描述:外围驱动器与原件 - PCI PCI Exp-PCI Bus Trans Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XIO2200GGW | 功能描述:IC PCI-EXPRESS/BUS BRIDGE 176BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| XIO2200ZGW | 功能描述:IC PCI-EXPRESS/BUS BRIDGE 176BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

发布紧急采购,3分钟左右您将得到回复。