参数资料

| 型号: | XIO2200AGGW |

| 厂商: | Texas Instruments |

| 文件页数: | 72/202页 |

| 文件大小: | 0K |

| 描述: | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| 产品培训模块: | PCI Express Basics |

| 标准包装: | 126 |

| 应用: | PCI Express 至 PCI 转换桥 |

| 接口: | PCI |

| 电源电压: | 1.35 V ~ 1.65 V,3 V ~ 3.6 V |

| 封装/外壳: | 176-LFBGA |

| 供应商设备封装: | 176-BGA MICROSTAR(15x15) |

| 包装: | 托盘 |

| 安装类型: | 表面贴装 |

| 产品目录页面: | 882 (CN2011-ZH PDF) |

| 配用: | XIO2200AEVM-ND - XIO2200AEVM |

| 其它名称: | 296-19617 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页

1394 OHCI Memory-Mapped Register Space

150

March 5 2007 June 2011

SCPS154C

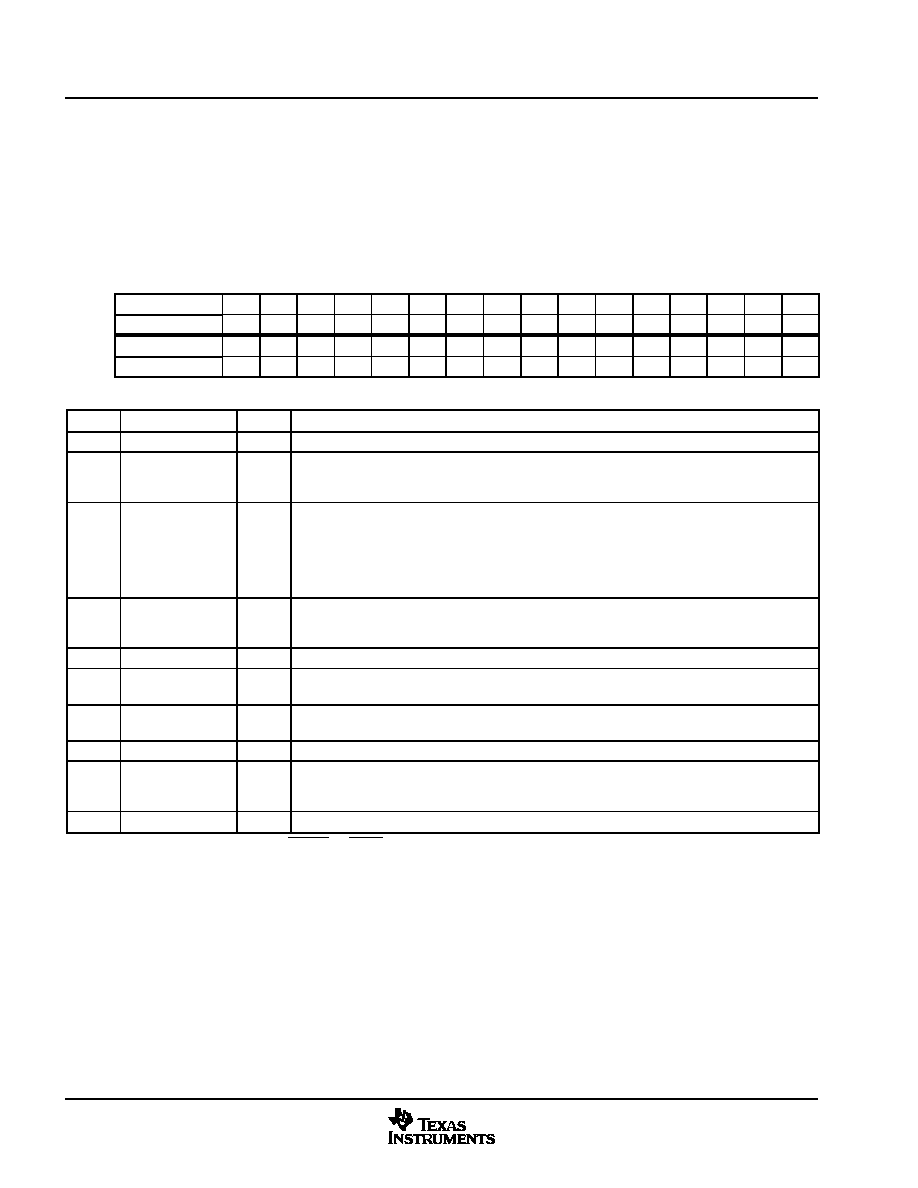

8.31 Link Control Register

The link control set/clear register provides the control flags that enable and configure the link core protocol

portions of the controller. It contains controls for the receiver and cycle timer. See Table 823 for a complete

description of the register contents.

OHCI register offset:

E0h set register

E4h clear register

Register type:

Read/Set/Clear/Update, Read/Set/Clear, Read-only

Default value:

00X0 0X00h

BIT NUMBER

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RESET STATE

0

X

0

BIT NUMBER

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RESET STATE

0

X

0

Table 823. Link Control Register Description

BIT

FIELD NAME

TYPE

DESCRIPTION

3123

RSVD

R

Reserved. Bits 3123 return 0 0000 0000b when read.

22

cycleSource

RSC

When bit 22 is set to 1b, the cycle timer uses an external source (CYCLEIN) to determine when to

roll over the cycle timer. When this bit is cleared, the cycle timer rolls over when the timer reaches

3072 cycles of the 24.576-MHz clock (125 μs).

21

cycleMaster

RSCU

When bit 21 is set to 1b, the controller is root and it generates a cycle start packet every time the cycle

timer rolls over, based on the setting of bit 22 (cycleSource). When bit 21 is cleared, the OHCI-Lynx

accepts received cycle start packets to maintain synchronization with the node which is sending

them. Bit 21 is automatically cleared when bit 25 (cycleTooLong) in the interrupt event register at

OHCI offset 80h/84h (see Section 8.21) is set to 1b. Bit 21 cannot be set to 1b until bit 25

(cycleTooLong) is cleared.

20

CycleTimerEnable

RSC

When bit 20 is set to 1b, the cycle timer offset counts cycles of the 24.576-MHz clock and rolls over

at the appropriate time, based on the settings of the above bits. When this bit is cleared, the cycle

timer offset does not count.

1911

RSVD

R

Reserved. Bits 1911 return 0 0000 0000b when read.

10

RcvPhyPkt

RSC

When bit 10 is set to 1b, the receiver accepts incoming PHY packets into the AR request context if

the AR request context is enabled. This bit does not control receipt of self-identification packets.

9

RcvSelfID

RSC

When bit 9 is set to 1b, the receiver accepts incoming self-identification packets. Before setting this

bit to 1b, software must ensure that the self-ID buffer pointer register contains a valid address.

87

RSVD

R

Reserved. Bits 8 and 7 return 00b when read.

6

tag1SyncFilterLock

RS

When bit 6 is set to 1b, bit 6 (tag1SyncFilter) in the isochronous receive context match register (see

Section 8.46) is set to 1b for all isochronous receive contexts. When bit 6 is cleared, bit 6

(tag1SyncFilter) in the isochronous receive context match register has read/write access.

50

RSVD

R

Reserved. Bits 50 return 00 0000b when read.

This bit is reset by a PCI Express reset (PERST), a GRST, or the internally-generated power-on reset.

Not Recommended for New Designs

相关PDF资料 |

PDF描述 |

|---|---|

| XIO2200AZGW | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| XPC823ZT81B2T | IC MPU POWERQUICC 81MHZ 256-PBGA |

| XPC8240RZU250E | MCU HOST PROCESSOR 352-TBGA |

| XQ6SLX150T-3CSG484I | IC FPGA SPARTAN-6Q 484-CSBGA |

| XR16C2550IJ-F | IC UART FIFO 16B DUAL 44PLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XIO2200AZGW | 功能描述:外围驱动器与原件 - PCI PCI Exp-PCI Bus Trans Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XIO2200AZGW | 制造商:Texas Instruments 功能描述:PCI Express to PCI Bus Converter IC |

| XIO2200AZHH | 功能描述:外围驱动器与原件 - PCI PCI Exp-PCI Bus Trans Bridge RoHS:否 制造商:PLX Technology 工作电源电压: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:FCBGA-1156 封装:Tray |

| XIO2200GGW | 功能描述:IC PCI-EXPRESS/BUS BRIDGE 176BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

| XIO2200ZGW | 功能描述:IC PCI-EXPRESS/BUS BRIDGE 176BGA RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:- 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2 |

发布紧急采购,3分钟左右您将得到回复。