- 您现在的位置:买卖IC网 > PDF目录16514 > XR17V252IM-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V252 100TQFP PDF资料下载

参数资料

| 型号: | XR17V252IM-0A-EVB |

| 厂商: | Exar Corporation |

| 文件页数: | 19/69页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V252 100TQFP |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页

XR17V252

26

66 MHZ PCI BUS DUAL UART WITH POWER MANAGEMENT SUPPORT

REV. 1.0.2

3.1.1

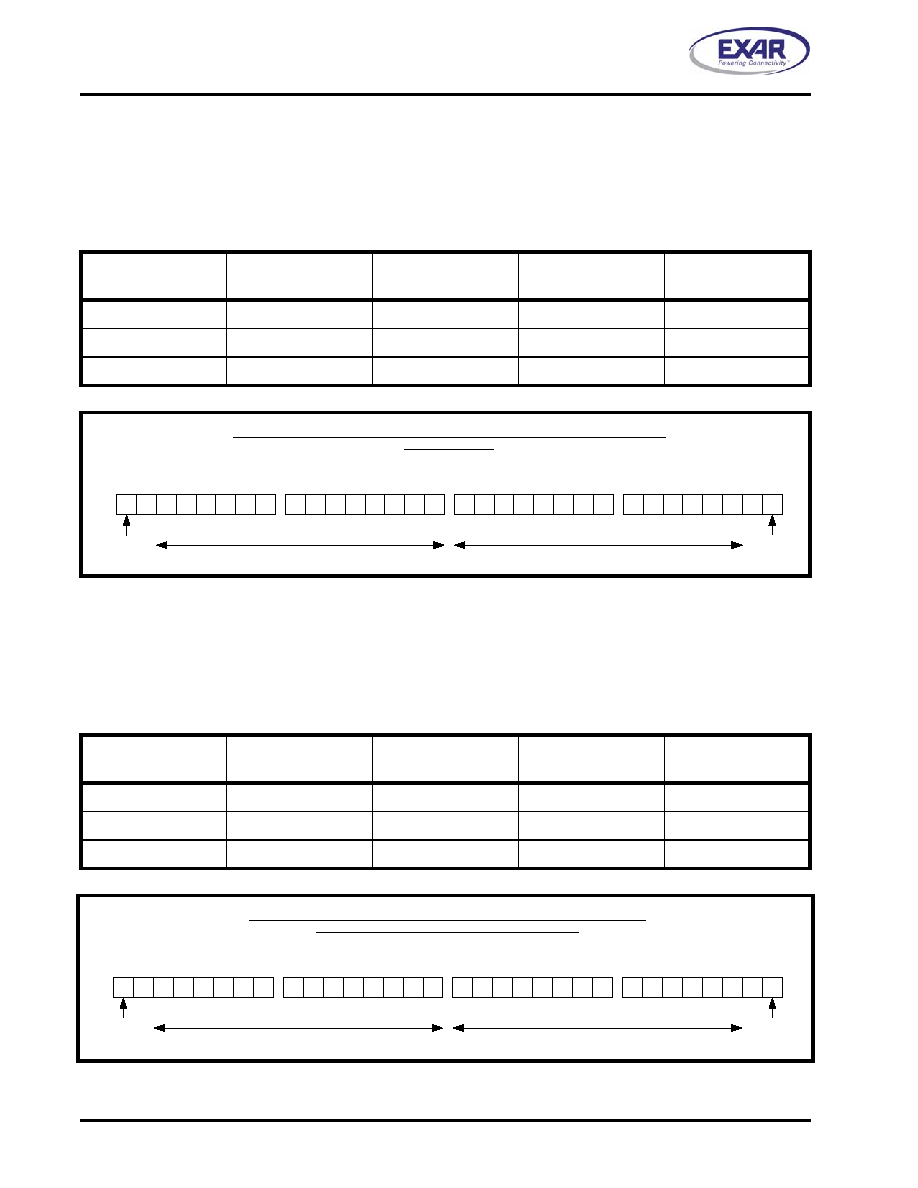

Normal Rx FIFO Data Unloading at locations 0x100 (channel 0) and 0x300 (channel 1)

The RX FIFO data (up to the maximum 64 bytes) can be read out in a single burst 32-bit read operation

(maximum 16 DWORD reads) at memory locations 0x100 (channel 0) and 0x300 (channel 1). This operation is

at least 16 times faster than reading the data in 64 separate 8-bit memory reads of RHR register (0x000 for

channel 0 and 0x200 for channel 1).

3.1.2

Special Rx FIFO Data Unloading at locations 0x180 (channel 0) and 0x380 (channel 1)

The XR17D152 also provides the same RX FIFO data along with the LSR status information of each byte side-

by-side, at locations 0x180 (channel 0) and 0x380 (channel 1). The entire RX data along with the status can be

downloaded in a single PCI Burst Read operation of 32 DWORD reads. The Status and Data bytes must be

read in 16 or 32 bits format to maintain data integrity. The following tables show this clearly.

READ RX FIFO,

WITH NO ERRORS

BYTE 3

BYTE 2

BYTE 1

BYTE 0

Read n+0 to n+3

FIFO Data n+3

FIFO Data n+2

FIFO Data n+1

FIFO Data n+0

Read n+4 to n+7

FIFO Data n+7

FIFO Data n+6

FIFO Data n+5

FIFO Data n+4

Etc.

READ RX FIFO,

WITH LSR

ERRORS

BYTE 3

BYTE 2

BYTE 1

BYTE 0

Read n+0 to n+1

FIFO Data n+1

LSR n+1

FIFO Data n+0

LSR n+0

Read n+2 to n+3

FIFO Data n+3

LSR n+3

FIFO Data n+2

LSR n+2

Etc

PCI Bus

Data Bit-31

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

Receive Data Byte n+3

Receive Data Byte n+2

Receive Data Byte n+1

Receive Data Byte n+0

PCI Bus

Data Bit-0

Channel 0 to 1 ReceiveData in 32-bit alignment through the Configuration Register Address

0x0100 and 0x0300

PCI Bus

Data Bit-31

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

Receive Data Byte n+1

Line Status Register n+1

Receive Data Byte n+0

Line Status Register n+0

PCI Bus

Data Bit-0

Channel 0 to 1 Receive Data with Line Status Register in a 32-bit alignment through

the Configuration Register Address 0x0180 and 0x0380

相关PDF资料 |

PDF描述 |

|---|---|

| 6278890-4 | C/A 62.5 OFNR MTRJ-MTRJ RED SEC |

| 6374656-4 | C/A LC TO LC MM 2.0MM 4M |

| VE-J5R-EX | CONVERTER MOD DC/DC 7.5V 75W |

| RBC26DRXN | CONN EDGECARD 52POS DIP .100 SLD |

| RBM15DTMN | CONN EDGECARD 30POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR17V252IM-F | 功能描述:UART 接口集成电路 66MHz Dual PCI UART RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| XR17V252IMTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 64Byte FIFO 3.3V 100-Pin TQFP T/R 制造商:Exar Corporation 功能描述:XR17V252IMTR-F |

| XR17V254 | 制造商:EXAR 制造商全称:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

| XR17V254_08 | 制造商:EXAR 制造商全称:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

| XR17V254IV | 制造商:EXAR 制造商全称:EXAR 功能描述:66MHZ PCI BUS QUAD UART WITH POWER MANAGEMENT SUPPORT |

发布紧急采购,3分钟左右您将得到回复。