- 您现在的位置:买卖IC网 > PDF目录16527 > XR20V2172L64-0B-EB (Exar Corporation)EVAL BOARD FOR XR20V2170 64QFN PDF资料下载

参数资料

| 型号: | XR20V2172L64-0B-EB |

| 厂商: | Exar Corporation |

| 文件页数: | 51/51页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR20V2170 64QFN |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页当前第51页

XR20V2172

9

REV. 1.0.2

TWO CHANNEL I2C/SPI UART WITH 64-BYTE FIFO AND RS232 TRANSCEIVER

2.2.1

SPI Bus Interface

The SPI interface consists of four lines: serial clock (SCL), chip select (CS#), slave output (SO) and slave input

(SI). The serial clock, slave output and slave input can be as fast as 18 MHz at 3.3V. To access the device in

the SPI mode, the CS# signal for the V2172 is asserted by the SPI master, then the SPI master starts toggling

the SCL signal with the appropriate transaction information. The first byte sent by the SPI master includes

whether it is a read or write transaction and the UART register being accessed. See Table 3 below.

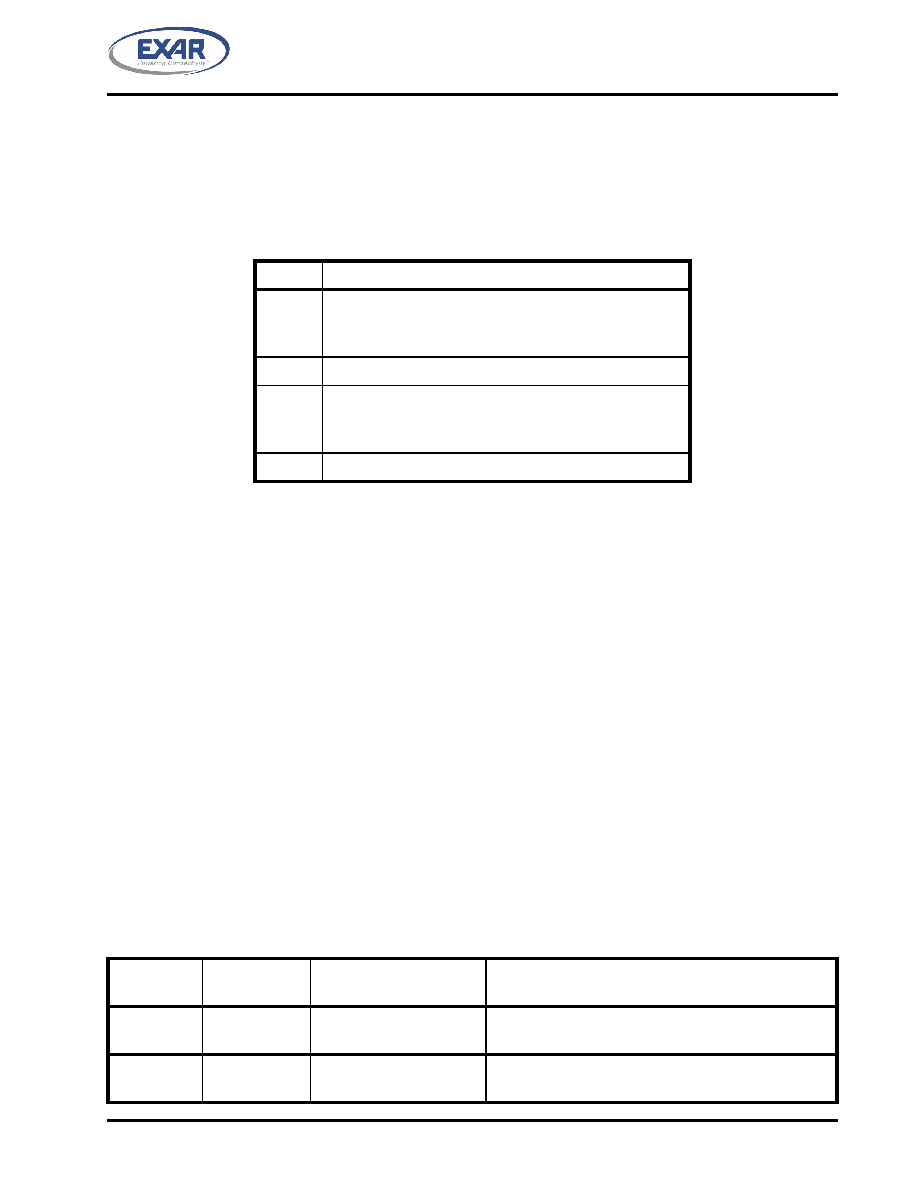

TABLE 3: SPI FIRST BYTE FORMAT

BIT

FUNCTION

7

Read/Write#

Logic 1 = Read

Logic 0 = Write

6:3

UART Internal Register Address A3:A0

2:1

UART Channel Select

’00’ = UART Channel A

’01’ = UART Channel B

0

Reserved

After the last read or write transaction, the SPI master will set the SCL signal back to its idle state (LOW).

2.3

Device Reset

The RESET# input resets the internal registers and the serial interface outputs in the UART to its default state

(see Table 16). An active low pulse of longer than 40 ns duration will be required to activate the reset function

in the device.

2.4

Internal Registers

The V2172 has a set of enhanced registers for control, monitoring and data loading and unloading. The

configuration register set is compatible to the industry standard ST16C550. These registers function as data

holding registers (THR/RHR), interrupt status and control registers (ISR/IER), a FIFO control register (FCR),

receive line status and control registers (LSR/LCR), modem status and control registers (MSR/MCR),

programmable data rate (clock) divisor registers (DLL/DLM/DLD), and a user accessible Scratchpad Register

(SPR).

Beyond the general 16C550 features and capabilities, the V2172 offers enhanced feature registers (EFR, Xon/

Xoff 1, Xon/Xoff 2, TCR, TLR, TXLVL, RXLVL, IODir, IOState, IOIntEna, IOControl, EFCR and DLD) that

provide automatic RTS and CTS hardware flow control, Xon/Xoff software flow control, TX and RX FIFO level

counters, and programmable FIFO trigger level control. All the register functions are discussed in full detail

2.5

IRQ# Output

The IRQ# interrupt output changes according to the operating mode and enhanced features setup. Table 4

and 5 summarize the operating behavior for the transmitter and receiver.

TABLE 4: IRQ# PIN OPERATION FOR TRANSMITTER

Auto RS485

Mode

FCR BIT-0 = 0

(FIFO DISABLED)

FCR BIT-0 = 1 (FIFO ENABLED)

IRQ# Pin

NO

HIGH = a byte in THR

LOW = THR empty

HIGH = FIFO above trigger level

LOW = FIFO below trigger level or FIFO empty

IRQ# Pin

YES

HIGH = a byte in THR

LOW = transmitter empty

HIGH = FIFO above trigger level

LOW = FIFO below trigger level or transmitter empty

相关PDF资料 |

PDF描述 |

|---|---|

| UPM1E181MPD6TD | CAP ALUM 180UF 25V 20% RADIAL |

| AQ1051N8S-T | INDUCTOR 1.8NH 760MA 0402 SMD |

| UPS2G3R3MPD1TD | CAP ALUM 3.3UF 400V 20% RADIAL |

| XR20V2172L64-0A-EB | EVAL BOARD FOR XR20V2170 64QFN |

| UPJ1C331MPD6TD | CAP ALUM 330UF 16V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XR-210 | 制造商:EXAR 制造商全称:EXAR 功能描述:FSK MODULATOR / DEMODULATOR |

| XR-2100CJ | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MODEM |

| XR-2100CP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:MODEM |

| XR-2103 | 制造商:EXAR 制造商全称:EXAR 功能描述:FSK Modem Filter |

| XR-2103A | 制造商:EXAR 制造商全称:EXAR 功能描述:FSK Modem Filter |

发布紧急采购,3分钟左右您将得到回复。