参数资料

| 型号: | XRT72L71IQ |

| 厂商: | Exar Corporation |

| 文件页数: | 94/102页 |

| 文件大小: | 0K |

| 描述: | IC FRAMER DS3 ATM UNI 160PQFP |

| 产品变化通告: | XRT72Lx Series Obsolescence 02/May/2012 |

| 标准包装: | 24 |

| 控制器类型: | DS3 ATM UNI,透明通道调帧器 |

| 电源电压: | 3.3V |

| 电流 - 电源: | 120mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 160-BQFP |

| 供应商设备封装: | 160-PQFP(28x28) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页当前第94页第95页第96页第97页第98页第99页第100页第101页第102页

á

XRT72L71

DS3 ATM UNI/CLEAR CHANNEL FRAMER

REV. 1.1.0

87

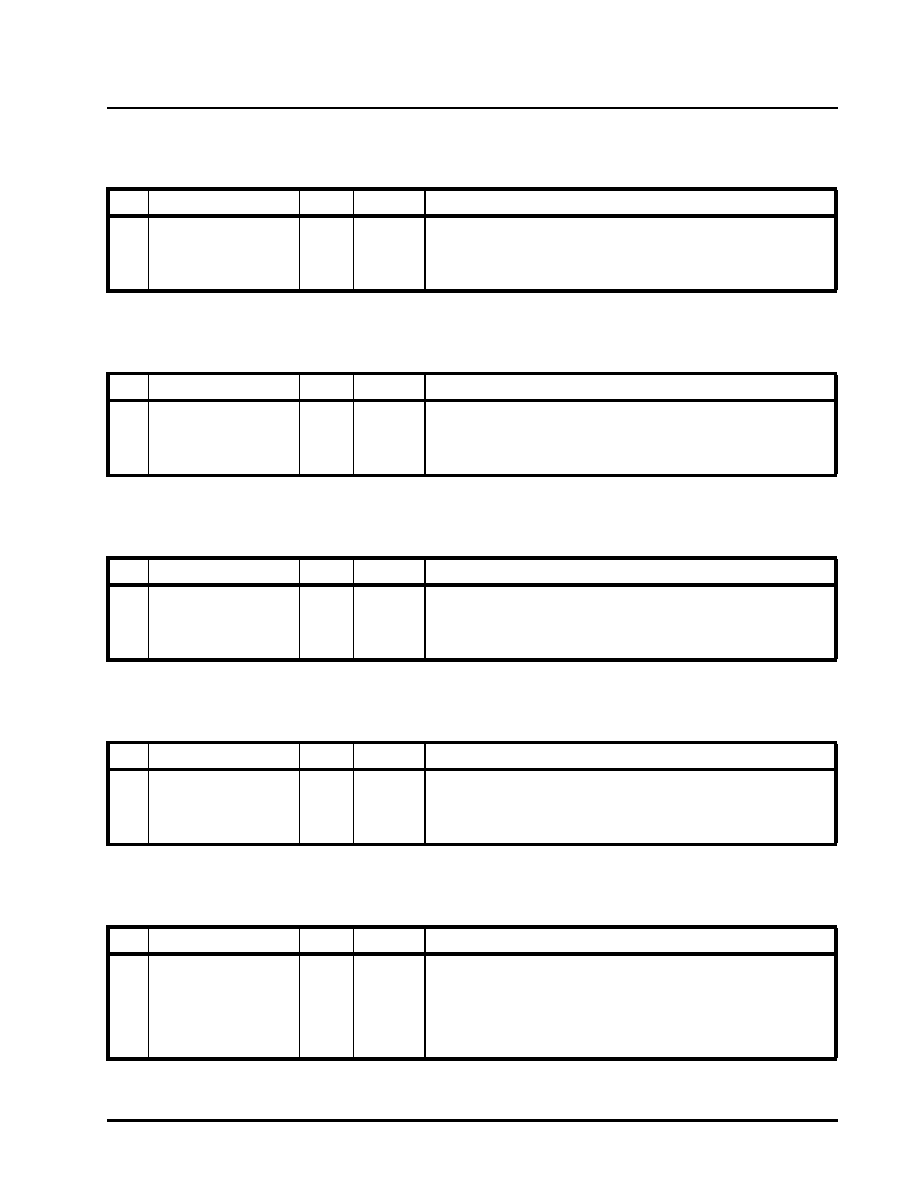

TABLE 102: TX CP IDLE CELL PATTERN HEADER BYTE-2

REGISTER 101

TX CP IDLE CELL PATTERN HEADER BYTE-2

HEX ADDRESS: 0X65

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

7-0

Tx Idle Cell Pattern 2

R/W

0x00

Contains pattern for the second header byte of each “outbound” idle cell.

Register is set to 0x00 when transmitting standard idle cell pattern.

NOTE: This bit-field is only active if the XRT72L71 is configured to operate

in the “ATM UNI” Mode.

TABLE 103: TX CP IDLE CELL PATTERN HEADER BYTE-3

REGISTER 102

TX CP IDLE CELL PATTERN HEADER BYTE-3

HEX ADDRESS: 0X66

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

7-0

Tx Idle Cell Pattern 3

R/W

0x00

Contains pattern for the third header byte of each “outbound” idle cell.

Register is set to 0x00 when transmitting standard idle cell pattern.

NOTE: This bit-field is only active if the XRT72L71 is configured to operate

in the “ATM UNI” Mode.

TABLE 104: TX CP IDLE CELL PATTERN HEADER BYTE-4

REGISTER 103

TX CP IDLE CELL PATTERN HEADER BYTE-4

HEX ADDRESS: 0X67

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

7-0

Tx Idle Cell Pattern 4

R/W

0x01

Contains pattern for the fourth header byte of each “outbound” idle cell.

Register is set to 0x01 when transmitting standard idle cell pattern.

NOTE: This bit-field is only active if the XRT72L71 is configured to operate

in the “ATM UNI” Mode.

TABLE 105: TX CP IDLE CELL PATTERN HEADER BYTE-5

REGISTER 104

TX CP IDLE CELL PATTERN HEADER BYTE-5

HEX ADDRESS: 0X68

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

7-0

Tx Idle Cell Pattern 5

R/W

0x52

Contains pattern for the fifth header byte of each “outbound” idle cell.

Register is set to 0x00 when transmitting standard idle cell pattern.

NOTE: This bit-field is only active if the XRT72L71 is configured to operate

in the “ATM UNI” Mode.

TABLE 106: TX CP IDLE CELL PAYLOAD REGISTER

REGISTER 105

TX CP IDLE CELL PAYLOAD REGISTER

HEX ADDRESS: 0X69

BIT

FUNCTION

TYPE

DEFAULT

DESCRIPTION-OPERATION

7-0

Tx Idle Cell Payload

R/W

0x5A

This register contains the value of the payload bytes within each “outbound”

Idle Cell. The contents of this register will be repeated 48 times, when filling

the payload of each “outbound” Idle Cell. pRegister is set to 0x5A when

transmitting standard idle cell pattern.

NOTE: This bit-field is only active if the XRT72L71 is configured to operate

in the “ATM UNI” Mode.

相关PDF资料 |

PDF描述 |

|---|---|

| XRT73L02MIV-F | IC LIU E3/DS3/STS-1 2CH 100TQFP |

| XRT73L03BIV-F | IC LIU E3/DS3/STS-1 3CH 120LQFP |

| XRT73L04BIV-F | IC LIU E3/DS3/STS-1 4CH 144LQFP |

| XRT73L06IB-F | IC LIU E3/DS3/STS-1 6CH 217BGA |

| XRT73LC00AIV-F | IC LIU STS1/DS3/E3 SGL 44TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRT72L71IQ-F | 功能描述:网络控制器与处理器 IC Single CH DS3 UNI (3.3V) RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

| XRT72L73IB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XRT72L74IB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Telecommunication IC |

| XRT7300 | 制造商:EXAR 制造商全称:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT |

| XRT7300ES | 功能描述:网络控制器与处理器 IC RoHS:否 制造商:Micrel 产品:Controller Area Network (CAN) 收发器数量: 数据速率: 电源电流(最大值):595 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:PBGA-400 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。