参数资料

| 型号: | AD5522JSVDZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 32/64页 |

| 文件大小: | 0K |

| 描述: | IC PMU QUAD 16BIT DAC 80-TQFP |

| 产品变化通告: | Improve FI ac crosstalk |

| 设计资源: | Parametric Measurement Unit and Supporting Components for PAD Appls Using AD5522 and AD7685 (CN0104) |

| 标准包装: | 1 |

| 类型: | 每引脚参数测量单元(PPMU) |

| 应用: | 自动测试设备 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 80-TQFP 裸露焊盘 |

| 供应商设备封装: | 80-TQFP(12x12) |

| 包装: | 托盘 |

| 产品目录页面: | 798 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页

AD5522

Data Sheet

Rev. E | Page 38 of 64

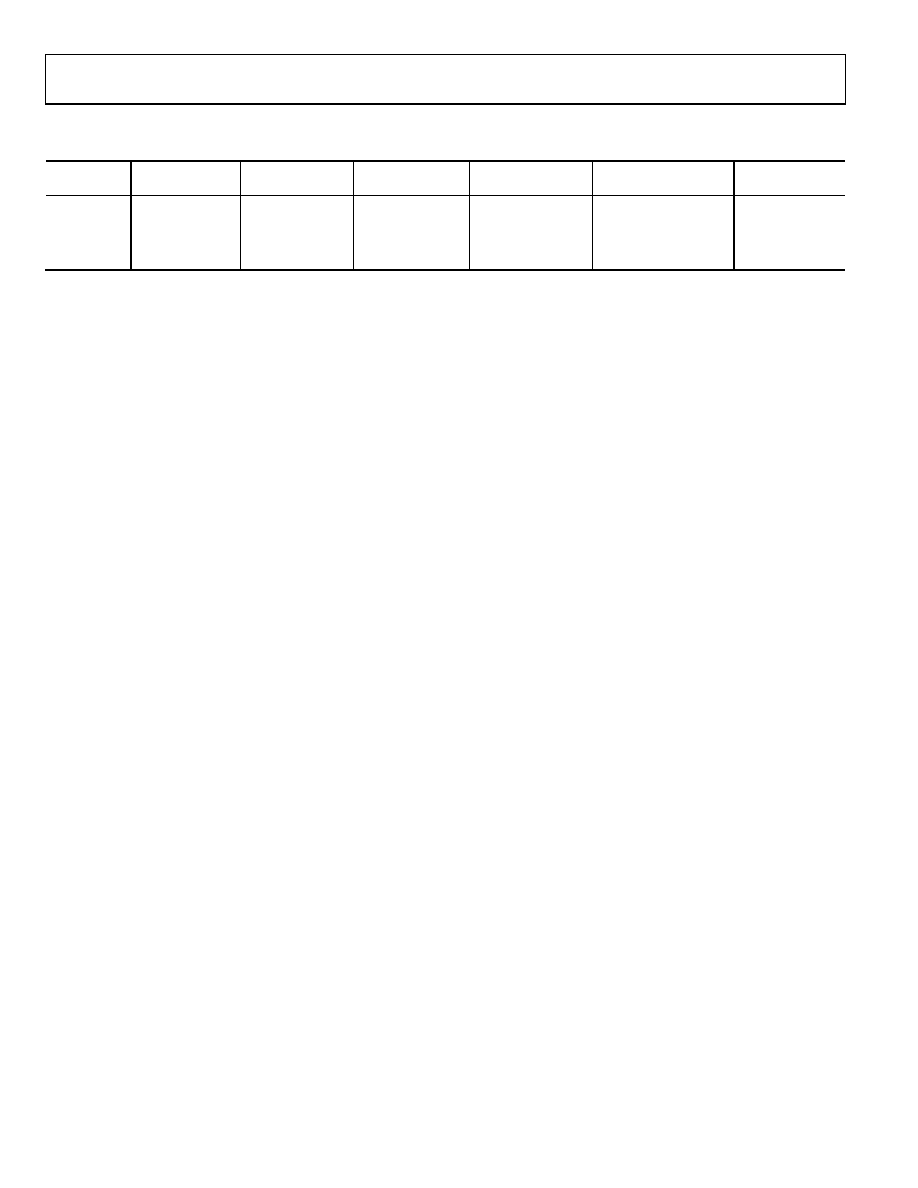

Table 14. References Suggested For Use with AD55221

Part No.

Voltage (V)

Initial

Accuracy %

Ref Out

TC (ppm/°C)

Ref Output

Current (mA)

SupplyVoltage

Range (V)

Package

ADR435

5

±0.04

1

30

+7 to +18

MSOP, SOIC

ADR445

5

±0.04

1

10

+5.5 to +18

MSOP, SOIC

ADR431

2.5

±0.04

1

30

+4.5 to +18

MSOP, SOIC

ADR441

2.5

±0.04

1

10

+3 to +18

MSOP, SOIC

1

Subset of the possible references suitable for use with the AD5522. Visit www.analog.com for more options.

For other voltage and current ranges, the required reference

level can be calculated as follows:

1. Identify the nominal range required.

2. Identify the maximum offset span and the maximum gain

required on the full output signal range.

3. Calculate the new maximum output range, including the

expected maximum gain and offset errors.

4. Choose the new required VOUTMAX and VOUTMIN, keeping

the VOUT limits centered on the nominal values. Note that

AVDD and AVSS must provide sufficient headroom.

5. Calculate the value of VREF as follows:

VREF = (VOUTMAX VOUTMIN)/4.5

Reference Selection Example

If, given the following conditions:

Nominal output range = 10 V (2 V to +8 V)

Offset error = ±100 mV

Gain error = ±0.5%

REFGND = AGND = 0 V

Then, with gain error = ±0.5%, the maximum positive gain

error = +0.5%, and the output range including gain error =

10 V + 0.005(10 V) = 10.05 V.

With offset error = ±100 mV, the maximum offset error span =

2(100 mV) = 0.2 V, and the output range including gain error

and offset error = 10.05 V + 0.2 V = 10.25 V.

To calculate VREF with actual output range = 10.25 V, that is,

2.125 V to +8.125 V (centered),

VREF = (8.125 V + 2.125 V)/4.5 = 2.28 V

If the solution yields an inconvenient reference level, the user

can adopt one of the following approaches:

Use a resistor divider to divide down a convenient, higher

reference level to the required level.

Select a convenient reference level above VREF and modify

the gain and offset registers to digitally downsize the reference.

In this way, the user can use almost any convenient refer-

ence level.

Use a combination of these two approaches.

In this case, the optimum reference is a 2.5 V reference; the user

can use the M and C registers and the offset DAC to achieve the

required 2 V to +8 V range. Change the ISENSE amplifier gain to

5 to ensure a full-scale current range of the specified values (see

the Current Range Selection section). This gain also allows opti-

mization of power supplies and minimizes power consumption

within the device.

It is important to bear in mind when choosing a reference value

that values other than 5 V (MI gain = 10) and 2.5 V (MI gain = 5)

result in current ranges other than those specified. See the

Measure Current Gains section for more details.

CALIBRATION

Calibration involves determining the gain and offset of each

channel in each mode and overwriting the default values in the

M and C registers of the individual DACs. In some cases (for

example, FI mode), the calibration constants, particularly those

for gains, may be range dependent.

Reducing Zero-Scale Error

Zero-scale error can be reduced as follows:

1. Set the output to the lowest possible value.

2. Measure the actual output voltage and compare it to the

required value. This gives the zero-scale error.

3. Calculate the number of LSBs equivalent to the zero-scale

error and add/subtract this number to the default value of

the C register.

Reducing Gain Error

Gain error can be reduced as follows:

1. Measure the zero-scale error.

2. Set the output to the highest possible value.

3. Measure the actual output voltage and compare it to the

required value. This is the gain error.

4. Calculate the number of LSBs equivalent to the gain error

and subtract this number from the default value of the M

register. Note that only positive gain error can be reduced.

相关PDF资料 |

PDF描述 |

|---|---|

| ESC65DRTI | CONN EDGECARD 130PS DIP .100 SLD |

| AMC30DRTS | CONN EDGECARD 60POS .100 DIP SLD |

| AMC30DRES | CONN EDGECARD 60POS .100 EYELET |

| ASC31DRAS | CONN EDGECARD 62POS .100 R/A DIP |

| RGM40DTMT | CONN EDGECARD 80POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5522JSVUZ | 功能描述:IC PMU QUAD 16BIT DAC 80-TQFP RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| AD5522JSVUZ-RL | 功能描述:Per-Pin Parametric Measurement Unit (PPMU) IC Automatic Test Equipment 80-TQFP-EP (12x12) 制造商:analog devices inc. 系列:- 包装:带卷(TR) 零件状态:有效 类型:每引脚参数测量单元(PPMU) 应用:自动测试设备 安装类型:表面贴装 封装/外壳:80-TQFP 裸露焊盘 供应商器件封装:80-TQFP-EP(12x12) 标准包装:1,000 |

| AD5523JCPZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad Parametric Measurement Unit With Integrated 16-Bit Level Setting DACs |

| AD5530 | 制造商:AD 制造商全称:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit DACs |

| AD5530_07 | 制造商:AD 制造商全称:Analog Devices 功能描述:Serial Input, Voltage Output 12-/14-Bit Digital-to-Analog Converters |

发布紧急采购,3分钟左右您将得到回复。