- 您现在的位置:买卖IC网 > PDF目录373890 > AD6623PCB (Analog Devices, Inc.) 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP PDF资料下载

参数资料

| 型号: | AD6623PCB |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | 4-Channel, 104 MSPS Digital Transmit Signal Processor TSP |

| 中文描述: | 4通道,104 MSPS的数字传输信号处理器判刑 |

| 文件页数: | 27/40页 |

| 文件大小: | 381K |

| 代理商: | AD6623PCB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6623

–27–

Sync bits are set low (External Address 5). All appropriate

control and memory registers (filter) are then loaded. The

Start Update Hold-Off Counter (0xn00) should be set to 0.

2. Set the appropriate program and sleep bits low (Ext Address 4).

This enables the channel. The channel must have Program

and Sleep Mode low to activate a channel.

32

NCO SHADOW

REGISTER

Q

D

Q

D

NCO

REGISTER

NCO PHASE

ACCUMULATOR

32

32

ENA

16

Q

D

Q

D

D

PL

PL

D

Q

CLR

SET

SLEEP

HOP

HOLDOFF

HOP

SYNC

START

HOLDOFF

HOLDOFF

COUNTER

START

COUNTER

RESET PIN

CLK

START

SYNC

16

16

16

CLR

C = 1

C = 0

ENA

C = 1

C = 0

ENA

M

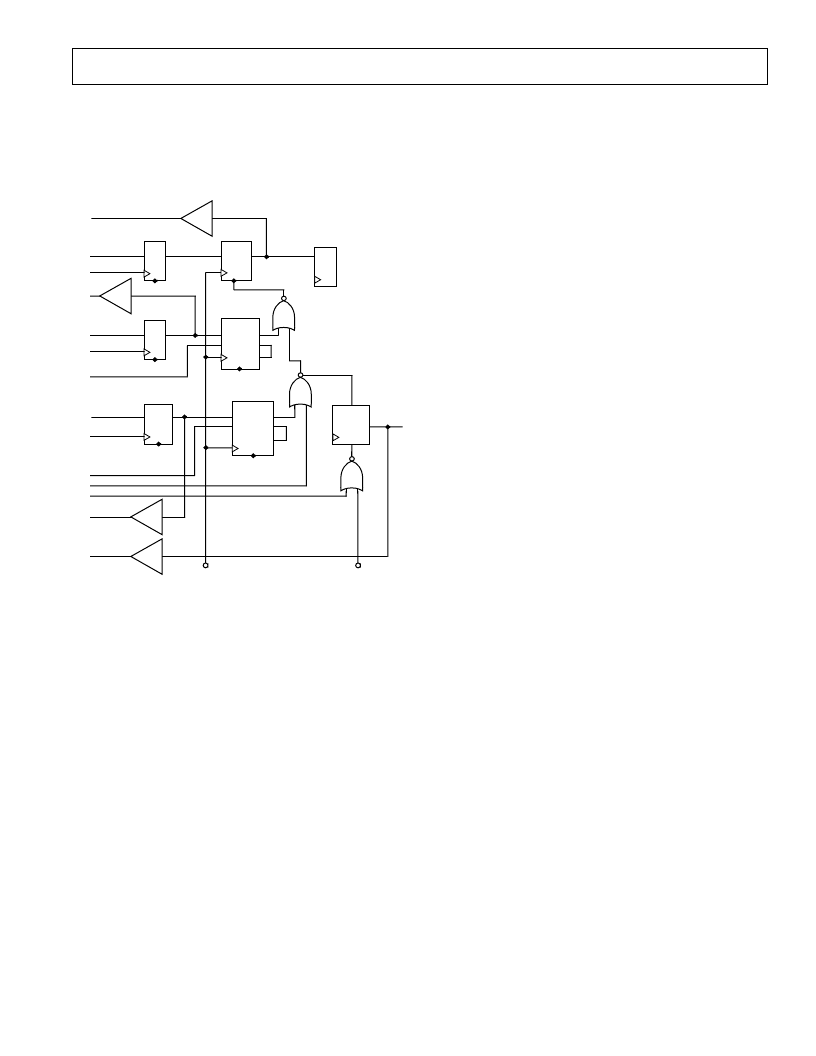

Figure 34. NCO Shadow Register and Hold-Off Counter

Start with Soft Sync

The AD6623 includes the ability to synchronize channels or chips

under microprocessor control. One action to synchronize is the

start of channels or chips. The Start Update Hold-Off Counter

(0xn00) in conjunction with the Start bit and Sync bit (Ext

Address 5) allow this synchronization. Basically the Start Update

Hold-Off Counter delays the Start of a channel(s) by its value

(number of AD6623 CLKs). The following method is used to syn-

chronize the start of multiple channels via microprocessor control.

1. Set the appropriate channels to sleep mode (a hard reset to the

AD6623 Reset pin brings all four channels up in sleep mode).

2. Write the Start Update Hold-Off Counter(s) (0xn00) to the

appropriate value (greater than 1 and less than 2

16

–

1). If the

chip(s) is not initialized, all other registers should be loaded

at this step.

3. Write the Start bit and the SyncX(s) bit high (Ext Address 5).

4. This starts the Start Update Hold-Off Counter counting down.

The counter is clocked with the AD6623 CLK signal. When it

reaches a count of one the sleep bit of the appropriate channel(s)

is set low to activate the channel(s).

Start with Pin Sync

A Sync pin is provided on the AD6623 to provide the most

accurate synchronization, especially between multiple AD6623s.

Synchronization of start with an external signal is accomplished

with the following method.

1. Set the appropriate channels to sleep mode (a hard reset to the

AD6623 Reset pin brings all four channels up in sleep mode).

2. Write the Start Update Hold-Off Counter(s) (0xn00) to the

appropriate value (greater than 1 and less than 2

16

–

1). If the

chip(s) is not initialized, all other registers should be loaded

at this step.

3. Set the Start on Pin Sync bit and the appropriate Sync Pin

Enable high (0xn01).

4. When the Sync pin is sampled high by the AD6623 CLK this

enables the count down of the Start Update Hold-Off Counter.

The counter is clocked with the AD6623 CLK signal. When it

reaches a count of one the sleep bit of the appropriate channel(s)

is set low to activate the channel(s).

Hop

A jump from one NCO frequency to a new NCO frequency.

This

change in frequency can be synchronized via microprocessor

control or an external Sync signal as described below.

To set the NCO frequency without synchronization the following

method should be used.

Set Frequency No Hop

1. Set the NCO Frequency Hold-Off counter to 0.

2. Load the appropriate NCO frequency. The new frequency

will be immediately loaded to the NCO.

Hop with Soft Sync

The AD6623 includes the ability to synchronize a change in NCO

frequency of multiple channels or chips under microprocessor

control. The NCO Frequency Hold-Off counter (0xn03) in con-

junction

with the Hop bit and the Sync bit (Ext Address 5) allow

this

synchronization. Basically the NCO Frequency Hold-Off

counter

delays the new frequency from being loaded into the NCO

by its

value (number of AD6623 CLKs). The following method

is used

to synchronize a hop in frequency of multiple channels

via microprocessor control.

1. Write the NCO Frequency Hold-Off (0xn03) counter to the

appropriate value (greater than 1 and less then 2

16

–

1).

2. Write the NCO Frequency register(s) to the new desired

frequency.

3. Write the hop bit and the Sync(s) bit high (Ext Address 5).

4. This starts the NCO Frequency Hold-Off counter counting

down. The counter is clocked with the AD6623 CLK signal.

When it reaches a count of one the new frequency is loaded

into the NCO.

Hop with Pin Sync

A Sync pin is provided on the AD6623 to provide the most

accurate synchronization, especially between multiple AD6623s.

Synchronization of hopping to a new NCO frequency with an

external signal is accomplished with the following method.

1. Write the NCO Frequency Hold-Off counter(s) (0xn03) to

the appropriate value (greater than 1 and less than 2

16

–

1).

2. Write the NCO Frequency register(s) to the new desired

frequency.

3. Set the Hop on Pin Sync bit and the appropriate Sync Pin

Enable high (0xn01).

4. When the Sync pin is sampled high by the AD6623 CLK

this enables the count down of the NCO Frequency Hold-Off

counter. The counter is clocked with the AD6623 CLK signal.

When it reaches a count of one the new frequency is loaded into

the NCO.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6624AS | Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630AR | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6623S/PCB | 制造商:Analog Devices 功能描述:4-CH, 104 MSPS DGTL TRANSMIT SGNL PROCESSOR (TSP) 28SOIC - Bulk |

| AD6624 | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624A | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AABC | 制造商:Advanced Micro Devices 功能描述: |

| AD6624AABCZ | 功能描述:DIGITAL SIGNAL PROC 196 CSP-BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。